## Universite Catholique de Louvain École Polytechnique de Louvain

Département d'Électricité

# Synthèse de circuits logiques à ultra-basse consommation en technologie 65nm et régime sous-seuil

Application à un coprocesseur AES pour tag RFID intelligent

Promoteur: Professeur J.-D. Legat

Mémoire présenté en vue de l'obtention du grade d'ingénieur civil en électricité par

**Hocquet Cédric**

Louvain-la-Neuve Année académique 2008-2009

## Résumé

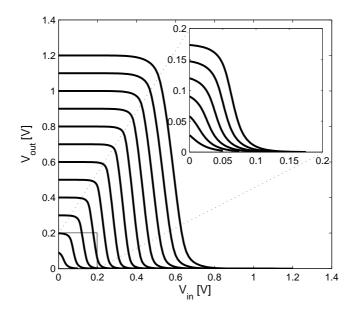

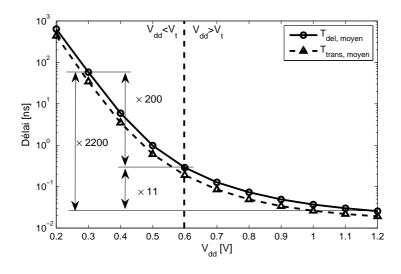

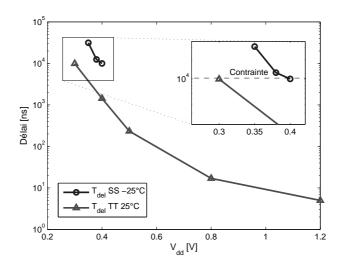

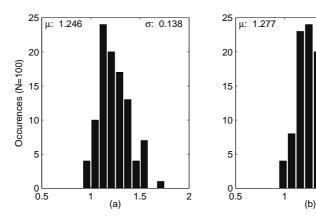

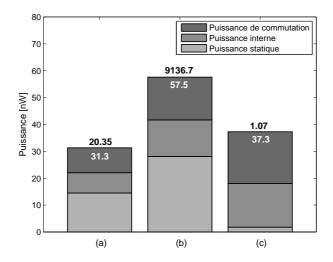

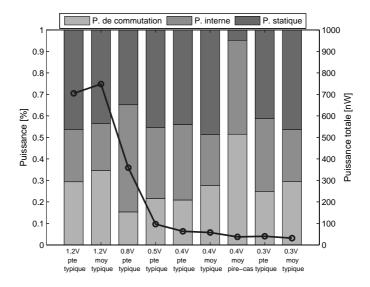

De nos jours, la technologie RFID est largement répandue. Les tags RFID intelligents doivent maintenant présenter des fonctionnalités de plus en plus avancées. Le chiffrement des données, permettant de sécuriser les transmissions qui se font sans-fil, est l'une de ces fonctionnalitées. Par ailleurs, le tag RFID est aussi fortement contraint en terme de consommation, en fonction de son type d'alimentation. L'objet de ce travail étant la synthèse de circuits logiques à très faible consommation en régime sous-seuil, l'étude est faite sur un coprocesseur AES, de manière à répondre aux besoins sus-cités. Dans une première approche, une analyse de l'inverseur de la bibliothèque de STMicroelectronics en 65nm est réalisée pour quantifier le comportement de celui-ci, en termes de délai et puissance principalement, à très faible  $V_{dd}$ . Le délai augmente d'un facteur 2000 lorsque  $V_{dd}$  diminue de 1.2V à 0.2V. La puissance est par contre réduite de six ordres de grandeur. Les effets de la variabilité sont aussi étudiés. À 0.2V, la variabilité gobale (process et température) implique une augmentation d'un facteur 24 du délai. Ensuite, pour synthétiser le circuit AES à très faible  $V_{dd}$ , une nouvelle bibliothèque de cellules est créée et caractérisée à différents faibles  $V_{dd}$ . À 100kHz, fréquence réaliste de fonctionnement du tag RFID compte tenu du protocole de communication, le coprocesseur AES est opérationnel jusqu'à une tension de 0.3V. Sa consommation vaut 31.3 nW. La variabilité globale (process et température) implique une augmentation de la tension minimum à 0.4V. Le consommation vaut alors 57.5 nW. La variabilité locale, implique une augmentation supplémentaire à 0.42V. Enfin, concernant la synthèse à très faible  $V_{dd}$ , deux résultats intérressants sont obtenus. Premièrement, alors qu'à la tension nominale (1.2V), l'outil de synthèse choisi uniquement les portes de plus petite taille pour réduire la consommation, cela n'est pas le cas à très faible  $V_{dd}$ . L'usage de portes de taille plus grande permet de diminuer la consommation en réduisant les courants de court-circuit grâce à la (dé)charge plus rapide des noeuds les plus conséquents. Cela permet un gain de puissance 17% sur le cirucit AES. Deuxièmement, la synthèse du circuit à l'aide d'une bibliothèque caractérisée à une très faible tension est plus optimale que celle réalisée à l'aide d'une bibliothèque caractérisée à la tension nominale, si le circuit doit être opéré à cette très faible tension. En effet, le tension minimum de fonctionnement du circuit synthétisé sera plus grande dans le deuxième cas, ce qui a pour conséquence d'augmenter la consommation minimale. Le gain en puissance est de 19% pour le coprocesseur AES.

## **Abstract**

Nowadays, the RFID technology is widely used for a large range of applications. Smart RFID tags, exhibit an increasing need of features to be packed within the chip. The encryption of the data, enabling secure wireless transmission, can be one of those features. Moreover, RFID tags are strongly power or energy constrained circuits then presenting a fixed small power or energy budget, depending on the power supply. The aim of the present work beeing the assessment of the synthesis of low-power logical circuits with subthreshold logic, the study is done on an AES coprocessor, in order to address the aforesaid needs. As a first approach, the simulation of the STMicroelectronics 65nm library inverter is realized to quantify its evolution when  $V_{dd}$  is lowered in terms of delay and power consumption. The delay increases by a factor 20 when  $V_{dd}$  is lowered from 1.2V to 0.2V. The power consumption instead is reduced by six orders of magnitude. The effects of the variability are also addressed. At 0.2V, the global variability (process and temperature) induces an increase of the delay by a factor 24. Afterwards, to synthesize the AES circuit at low- $V_{dd}$ , a new cells library is created and characterized at different low- $V_{dd}$ . At 100kHz, which is a realistic operating frequency for RFID tags in consideration of the communication protocol, the coprocessor is operationnal right down to  $V_{dd} = 0.3$ V. Its power consumption is 31.3 nW. Global variability (still process and temperature) requires the minimal voltage to be rised to 0.4V. The power consumption is then 57.5 nW. Local variability requires an additional increase of  $V_{dd}$  to 0.42V. Finally, two interesting results regarding the logical synthesis at low- $V_{dd}$ are reported. Firstly, while at nominal  $V_{dd}$  (1.2V) the synthesis tool chooses only the cells with the smallest driving strength in order to reduce the power consumption, this is not the case at low- $V_{dd}$ . The use of larger cells enables the reduction of the power consumption by decreasing the short-circuit currents thanks to the faster (dis)charge of some larger nodes. A gain of power consumption of 17% is reached for the AES circuit. Secondly, the synthesis of the circuit with a library characterized at low- $V_{dd}$  is more optimal than the synthesis of the circuit with a llibrary characterized at nominal  $V_{dd}$ , if the circuit is operated at that low- $V_{dd}$ . Indeed, the minimum supply voltage of the synthesized circuit is higher in the second case, increasing this way the minimum power consumption achievable. There is a difference of 19% in power consumption for the AES coprocessor.

## Table des matières

| 1 Introduction |                        |              |                                                    |    |  |  |  |

|----------------|------------------------|--------------|----------------------------------------------------|----|--|--|--|

| 2              | État de l'art          |              |                                                    |    |  |  |  |

|                | 2.1                    | Advan        | nced Encryption Standard                           | 5  |  |  |  |

|                |                        | 2.1.1        | Introduction                                       | 5  |  |  |  |

|                |                        | 2.1.2        | Architecture                                       | 6  |  |  |  |

|                |                        |              | 2.1.2.1 Architecture générale                      | 6  |  |  |  |

|                |                        |              | 2.1.2.2 Implémentations des différentes opérations | 7  |  |  |  |

|                |                        | 2.1.3        | Implémentation faible consommation                 | 8  |  |  |  |

|                |                        |              | 2.1.3.1 S-Box                                      | 8  |  |  |  |

|                |                        |              | 2.1.3.2 Co-processeur AES complet                  | 12 |  |  |  |

|                | 2.2 Logique sous-seuil |              |                                                    |    |  |  |  |

|                |                        | Introduction | 20                                                 |    |  |  |  |

|                |                        | 2.2.2        | Bibliothèque de cellules                           | 21 |  |  |  |

|                |                        | 2.2.3        | Variabilité                                        | 23 |  |  |  |

|                |                        | 2.2.4        | Résultats récents                                  | 24 |  |  |  |

|                | 2.3 Conclusion         |              |                                                    |    |  |  |  |

| 3              | Cara                   | actérisa     | ation des cellules                                 | 26 |  |  |  |

|                | 3.1                    | Introdu      | uction aux bibliothèques digitales                 | 26 |  |  |  |

|                                |        | 3.1.1                                      | Délai dans la bibliothèque                                                 | 27 |  |  |  |  |

|--------------------------------|--------|--------------------------------------------|----------------------------------------------------------------------------|----|--|--|--|--|

|                                |        | 3.1.2                                      | Puissance dans la bibliothèque                                             | 28 |  |  |  |  |

|                                | 3.2    | 2 Modélisation du délai et de la puissance |                                                                            |    |  |  |  |  |

|                                | 3.3    | Cas de                                     | l'inverseur                                                                | 31 |  |  |  |  |

|                                |        | 3.3.1                                      | Délai                                                                      | 32 |  |  |  |  |

|                                |        | 3.3.2                                      | Puissance et énergie                                                       | 33 |  |  |  |  |

|                                |        | 3.3.3                                      | Variabilité                                                                | 37 |  |  |  |  |

|                                | 3.4    | Flot de                                    | e caractérisation                                                          | 41 |  |  |  |  |

|                                | 3.5    | Conclu                                     | asion                                                                      | 41 |  |  |  |  |

| 4                              | Cop    | rocessei                                   | ur AES faible consommation                                                 | 43 |  |  |  |  |

|                                | 4.1    | Présen                                     | tation et validation fonctionnelle du coprocesseur AES                     | 43 |  |  |  |  |

|                                | 4.2    | Synthè                                     | ese à $V_{dd}$ nominal                                                     | 44 |  |  |  |  |

|                                | 4.3    | .3 Synthèse à très faible $V_{dd}$         |                                                                            |    |  |  |  |  |

|                                |        | 4.3.1                                      | Bibliothèque recaractérisée à basse tension                                | 47 |  |  |  |  |

|                                |        |                                            | 4.3.1.1 Choix des cellules                                                 | 47 |  |  |  |  |

|                                |        |                                            | 4.3.1.2 Influence de la taille des cellules                                | 48 |  |  |  |  |

|                                |        |                                            | 4.3.1.3 Influence de la bibliothèque recaractérisée à très faible $V_{dd}$ | 49 |  |  |  |  |

|                                |        | 4.3.2                                      | Influence de la variabilité                                                | 50 |  |  |  |  |

|                                |        | 4.3.3                                      | Résultats                                                                  | 51 |  |  |  |  |

|                                | 4.4    | Conclu                                     | asion                                                                      | 54 |  |  |  |  |

| 5                              | Con    | clusion                                    |                                                                            | 55 |  |  |  |  |

| Bi                             | bliogi | aphie                                      |                                                                            | 57 |  |  |  |  |

| A Advanced Encryption Standard |        |                                            |                                                                            |    |  |  |  |  |

|                                | A.1    | 1 L'algorithme                             |                                                                            |    |  |  |  |  |

|                                | A.2    | Les op                                     | érations                                                                   | 62 |  |  |  |  |

|                                |        | A.2.1                                      | L'opération SubBytes                                                       | 62 |  |  |  |  |

|                                |        | A 2 2                                      | L'onération ShiftRows                                                      | 62 |  |  |  |  |

|     |                |     |    | •    |    |

|-----|----------------|-----|----|------|----|

| TAI | $\mathbf{RLE}$ | DES | MA | TIÈR | ES |

**C** Publication

|   |                            | A.2.3   | L'opération MixColumns       | 63 |  |  |

|---|----------------------------|---------|------------------------------|----|--|--|

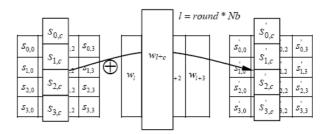

|   |                            | A.2.4   | L'opération AddRoundKey      | 63 |  |  |

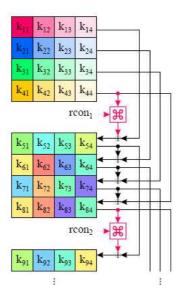

|   |                            | A.2.5   | Les clés de round            | 64 |  |  |

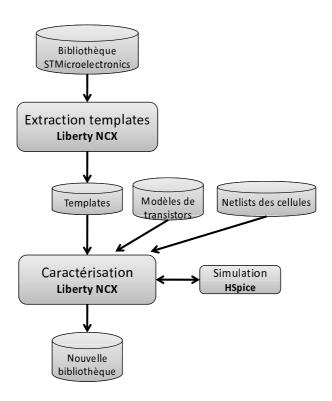

| В | Méthode de caractérisation |         |                              |    |  |  |

|   | B.1                        | Introdu | uction                       | 66 |  |  |

|   | B.2                        | Extrac  | tion des templates           | 67 |  |  |

|   | B.3                        | Caract  | érisation de la bibliothèque | 77 |  |  |

|   | B.4                        | Compi   | ilation de la bibliothèque   | 83 |  |  |

|   |                            |         |                              |    |  |  |

84

## Remerciements

Avant d'entrer dans le vif du sujet, je tiens à remercier plusieurs personnes qui ont contribuées à la réalisation de ce travail. Tout d'abord, je pense à mon promoteur, le Professeur Jean-Didier Legat, qui m'a encadré tout au long de l'année et dont les conseils avisés m'ont beaucoup aidés pour l'accomplissement de ce travail. Je tiens à le remercier tout particulièrement pour m'avoir fait confiance et m'avoir permis de participer aux journées FTFC.

Ensuite, je me dois de remercier David Bol, qui a toujours été là pour répondre à mes nombreuses questions et qui n'a jamais hésité à me consacrer de son temps lorsque cela était nécessaire. Ses conseils judicieux et son souci du détail m'auront beaucoup appris.

Merci aussi à Dina Kamel pour ses relectures et autres conseils utiles ainsi qu'à Bertrand Rousseau pour m'avoir briefé sur les bibliothèques ST. Enfin, merci à Philippe Manet et Thibault Delavallée qui m'ont "hébergé" durant ce quadrimestre et m'ont encouragé par les nombreuses discussions, formelles ou non, que j'ai pu avoir avec eux.

Pour terminer, merci à François Gosset et François-Xavier Standaert pour m'avoir fourni le code VHDL du coprocesseur AES.

En espérant n'avoir oublié personne, il ne me reste plus qu'à vous souhaiter une bonne lecture.

Cédric.

Frank M. Wanlass, à propos de l'inverseur CMOS dans son brevet de 1967.

|          |   | _ |   |  |  |  |

|----------|---|---|---|--|--|--|

|          | 1 |   | • |  |  |  |

|          |   |   |   |  |  |  |

|          |   |   |   |  |  |  |

|          |   |   |   |  |  |  |

| Chanitra |   |   |   |  |  |  |

| Chapitre |   | _ |   |  |  |  |

De nos jours, la technologie RFID (Radio Frequency IDentification) est de plus en plus utilisée. Le tag RFID, composé d'un petit circuit intégré et d'une antenne, le tout encapsulé dans un boîtier souvent très compact, permet, de par sa petite taille, de fournir un moyen pratique d'identification partout où cela est nécéssaire, lorsque ces tags sont utilisés en combinaison à un lecteur adéquat. Ainsi, les exemples ne manquent pas, du forfait de remontées-mécaniques en station de ski aux plaques de voitures électroniques, en passant par des systèmes de traçage des bagages en aéroport ou de gestion de chaînes logistiques en entrepôt. Mais toutes ces applications, de plus en plus nombreuses, nécéssitent bien souvent des fonctionnalités avancées, que se doit de fournir le petit circuit intégré du tag. C'est la raison pour laquelle on peut parler de tag RFID intelligent. Une de ces fonctionnalités peut être, par exemple, la possibilité de prendre des mesures de température pour contrôler la chaîne du froid d'un produit surgelé. Comme la technologie RFID échange des données de manière sans-fils, une autre de ces fonctionnalités, très importante, est la possibilité de sécuriser les données transitant par le tag. En effet, dès lors qu'un tag RFID peut être utilisé pour avoir accès à des biens (batiment, voiture) ou encore peut contenir des informations confidentielles (passeport, plaque de voiture), il est de plus en plus indispensable que les données transitant depuis ou vers le tag soient chiffrées. Ce travail, en proposant d'étudier la synthèse d'un module AES <sup>1</sup>, présente une telle solution de chiffrement.

De plus, alors que les dimensions du circuit intégré, et donc, en première approximation, sa consommation<sup>2</sup>, augmente pour inclure ces nouvelles fonctionnalités, le bugdet de puissance ou d'énergie alloué au tag RFID, lui, n'évolue pas et reste limité. Ce budget est fonction du type d'alimentation qui est en général fournie par une batterie ou via un champ

<sup>1.</sup> Advanced Encryption Standard, voir Annexe A

<sup>2.</sup> Nous verrons qu'un circuit de plus petite taille n'implique pas nécéssairement une consommation plus faible et inversement.

électro-magétique. Dès lors, il est indispensable de réduire la consommation du circuit à tout prix. Une des solutions pour parvenir à cette fin consiste à faire fonctionner le circuit à la tension d'alimentation  $V_{dd}$  la plus faible possible. Cette tension minimum, lorsque les contraintes imposées au circuit le permettent, peut se situer en dessous de la tension de seuil  $V_t$  des transistors. C'est pourquoi, on parle de fonctionnement en régime sous-seuil  $^3$ . C'est dans cette région sous-seuil que l'étude du module AES, proposée ici, est réalisée.

Ainsi, plus généralement, ce travail étudie la synthèse de circuits logiques en régime sous-seuil, le module AES servant de circuit "test" pour comparer les différentes synthèses. Les objectifs fixés à priori pour ce travail ont servi de fil conducteur pour mener à bien l'étude. Ils peuvent être divisés en deux groupes : d'une part, ceux ayant trait à la synthèse logique en générale :

- Déterminer si l'utilisation d'une bibliothèque caractérisée à la tension cible de fonctionnenemt du circuit est utile pour la synthèse de celui-ci. Autrement dit, il s'agit de comparer, en terme de puissance, les résultats de la synthèse du circuit avec une bibliothèque caractérisée à tension V<sub>dd</sub> nominale à ceux de la synthèse du circuit avec une bibliothèque caractérisée à faible tension V<sub>dd</sub>, lorsque le circuit est opéré à cette même faible tension V<sub>dd</sub>. Il s'agit là de l'objectif principal de ce mémoire.

- Observer l'influence de la taille des cellules que contient la bibliothèque sur la synthèse d'un circuit à faible  $V_{dd}$ .

et d'autre part, ceux propres au module AES faible consommation :

- Déterminer la tension  $V_{dd}$  minimum du module AES. Cette tension est determinée en choisissant d'abord une contrainte temporelle réaliste pour le circuit.

- Estimer la consommation du module AES à cette tension  $V_{dd}$  minimum.

Le point de départ de ce travail étant la biliothèque 65nm de STMicroelectronics ainsi que le code VHDL du coprocesseur AES, il a fallu passer par différentes étapes pour mener à bien le travail et parvenir à réaliser les objectifs. Détaillons ces différentes étapes. Tout d'abord, il a fallu procéder à l'étude de l'évolution d'une cellule simple de la bibliothèque 65nm lors de la réduction de  $V_{dd}$ . Dans un premier temps, les résultats fournis par la simulation de cette cellule simple à l'aide d'un outil de simulation de circuit analogique classique  $^4$  sont comparés aux valeurs trouvées dans la bibliothèque à tension nominale, en guise de vérification. Ensuite, il s'agit de simuler la cellule pour observer et quantifier l'évolution du délai, de la puissance et de l'énergie consommée lorsque  $V_{dd}$  diminue. La variabilité est aussi étudiée. La deuxième étape a été le développement d'une méthode de caractérisation. La caractérisation

<sup>3.</sup> Remarquons ici que le but premier est bien de réduire la consommation du circuit et non pas de le faire fonctionner systématiquement en régime sous-seuil, même si cela sera bien souvent le cas.

<sup>4.</sup> ELDO

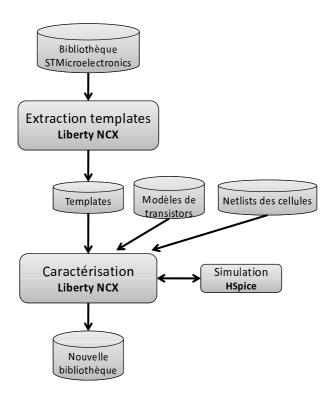

manuelle des cellules à l'aide du même outil de simulation s'est avérée compliqué, dû au grand nombre de paramètres à caractériser. Il a donc fallu trouver une solution réaliste pour caractériser une bibliothèque de cellules complète. C'est finalement l'outil Liberty NCX de Synopsys qui à été utilisé. L'apprentissage de ce dernier fût l'une des étapes majeures de ce travail  $^5$ . La caractérisation à proprement parler des bibliothèques basse-tensions a pû ensuite être réalisée. La méthode de caractérisation étant au point, il s'agit de choisir les cellules qui constitueront la bibliothèque, de les caractériser et de compiler la bibliothèque, cela pour différentes tensions  $V_{dd}$ . La dernière étape peut alors être entamée. Il s'agit de la synthèse du module AES avec les différentes bibliothèques recaractérisées. Il est maintenant possible d'observer l'évolution du module AES lorsque  $V_{dd}$  diminue. À partir de ces résultats, les conclusions peuvent être tirées quant aux objectifs posés. Il est bon d'indiquer que, pendant toutes ces différentes étapes, de nombreuses publications scientifiques ont dû être lues, analysées et critiquées afin de mieux comprendre la problèmatique étudiée. Enfin, ce travail à également été l'objet d'un papier soumis à l'occasion des huitièmes journées d'études Faible Tension Faible Consommation  $2009^6$ .

En guise d'avant-goût, nous pouvons d'ores et déjà révéler ici les principaux résultats :

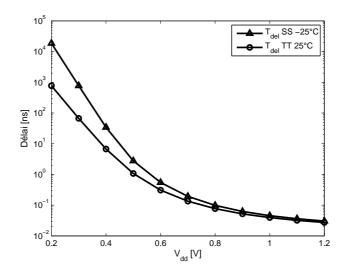

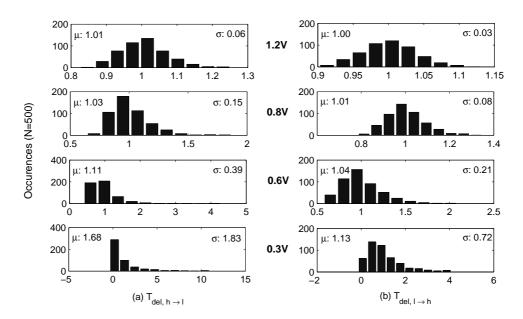

- La simulation de l'inverseur nous montre une augmentation du délai d'un facteur 2000 lorsque V<sub>dd</sub> passe de 1.2V à 0.2V. La puissance, grâce à la réduction de la fréquence, diminue quant à elle de six ordres de grandeur. La variabilité globale (process et témpérature) provoque une augmentation du délai d'un facteur 24 à 0.2V.

- A faible  $V_{dd}$ , la présence de cellules plus grandes dans la bibliothèque permet de diminuer la consommation interne grâce à la réduction des courants de court-circuit dûe à une (dé)charge plus rapide des noeuds. Un gain de l'ordre de 17% est observable. Cela n'est pas valable à la tension nominale.

- La synthèse à l'aide d'une bibliothèque caractérisée à la tension cible de fonctionnement du circuit est effectivement plus efficace et permet de réaliser un gain de l'ordre de 19%. Ce gain provient du fait que le circuit synthétisé à l'aide de la bibliothèque caractérisée à la tension nominale possède un V<sub>min</sub> supérieur à celui du circuit synthétisé avec la bibliothèque caractérisée à faible V<sub>dd</sub>.

- Le coprocesseur AES peut fonctionner à une tension d'alimentation de 0.3V avec une fréquence de 100kHz. Sa consommation est de 31.3 nW. En considérant la variabilité globale, il faut monter la tension à 0.4V pour que le circuit reste fonctionnel. Sa consommation augmente à 57.5 nW. La prise en compte de la variabilité locale implique une seconde augmentation de  $V_{dd}$  jusqu'à 0.42V.

<sup>5.</sup> En terme de temps y consacré.

<sup>6.</sup> Le papier est disponible en Annexe C.

Après ce premier chapitre d'introduction, le second propose un petit tour d'horizon des différents coprocesseurs AES réalisés jusqu'à présent et présentant une faible consommation. Dans le but de faire apparaître plus clairement le contexte dans lequel ce travail a été réalisé, une introduction à la logique sous-seuil et quelques-unes de ses applications récentes sont ensuite exposés. Le début du troisième chapitre est consacré à la présentation des bibliothèques digitales et à la manière dont les différents paramètres des cellules sont modèlisés au sein de celles-ci. Ensuite, la modélisation classique du délai et de la puissance est exposée. La suite du chapitre est consacré à l'étude d'un inverseur de la bibliothèque 65nm, lorsque la tension d'alimentation est diminuée. Plus particulièrement, l'évolution du délai, de la puissance et de l'énergie pas transition est présentée. Le comportement statique de l'inverseur est également montré ainsi que l'effet, négatif, de la variabilité globale et locale, amplifié à faible  $V_{dd}$ . Le quatrième chapitre présente les résultats de la synthèse du coprocesseur AES à l'aide des bibliothèques recaractérisées à faible  $V_{dd}$ . Les bibliothèques recaractérisées sont d'abord présentées, ensuite des réponses aux questions soulevées dans cette introduction sont proposées, principalement concerant l'utilité de la bibliothèque recaractérisée à faible  $V_{dd}$  ainsi que l'effet de la taille de cellules contenues dans les bibliothèques sur la synthèse. Finalement, le cinquième et dernier chapitre conclut le travail.

Cette section présente le contexte dans lequel ce travail a été réalisé afin d'en dégager certaines de ses motivations. Cela sera fait en relatant les travaux précédement effectués dans les domaines d'intérêt. La première section de ce chapitre détaille l'avancée des recherches scientifiques réalisées autour de l'implémentation basse consommation d'un coprocesseur AES. Après une rapide présentation de l'architecture générale d'un tel coprocesseur et de l'implémentation basique de ses différentes opérations, les travaux ayant pour objet l'optimisation de la S-Box suivi de ceux concernant l'optimisation du coprocesseur AES dans son ensemble sont exposés. La deuxième partie concerne de manière plus générale la logique sous-seuil. Une introduction à cette logique est d'abord proposée, ensuite quelques résultats récents de circuits utilisant cette logique sont détaillés.

## 2.1 Advanced Encryption Standard

#### 2.1.1 Introduction

Depuis l'adoption de l'algorithme *Rijndael* comme standard de chiffrement pour l'AES en 2000, et tel que présenté en Annexe A, bon nombre d'implémentations matérielles ont fait leur apparition. Comme pour tout circuit digital, deux grandes approches peuvent être distinguées. Il s'agit de la conception haute performance (en terme de vitesse) et de la conception faible surface/faible consommation. Dans le cadre de ce travail, la conception haute performance ne sera pas abordée, si ce n'est un survol rapide de son architecture générale. Le lecteur curieux peut se référer à [4], [1] et [5] pour les meilleurs résultats concernant la haute performance. Nous ne nous intéresserons donc qu'à la conception faible surface/faible consommation.

Une autre subdivision peut être également faite lorsque que l'on parle d'implémentation ma-

térielle. Celle-ci peut se faire à l'aide d'un circuit logique programmable (FPGA) ou bien directement comme circuit intégré spécialisé (ASIC). Ici, seule cette deuxième solution sera couverte.

La section suivante détaille l'architecture générale des coprocesseurs AES. Ensuite, les optimisations au niveau de la S-Box puis des coprocesseurs AES complets seront abordées au travers des différents travaux réalisés.

#### 2.1.2 Architecture

#### 2.1.2.1 Architecture générale

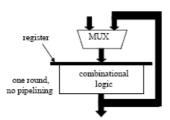

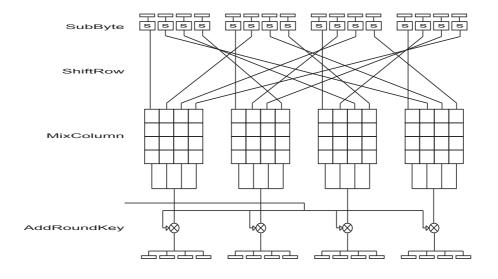

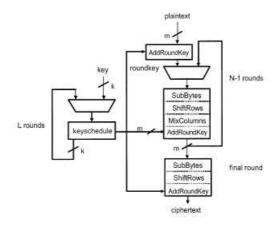

L'implémentation de base présente une architecture itérative dans laquelle se trouve du matériel pour un seul *round* <sup>1</sup> à la fois. La sortie est routée vers l'entrée du bloc pour réaliser les différentes itérations de la boucle. Cela est présenté à la Figure 1. Cette architecture basique ne permettra pas de réaliser un circuit haute performance à cause du grand nombre de cycles requis. On verra par la suite que ce sera par contre une architecture intéressante pour réduire la consommation.

**FIGURE 1:** Architecture itérative de base (source : [6])

Différentes techniques peuvent être utilisées pour améliorer cette première architecture :

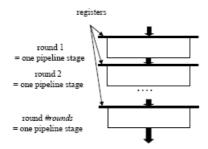

- Déroulage : L'architecture déroulée possède du matériel pour éxécuter plus d'un *round* à la fois. La boucle peut être partiellement ou complètement déroulée selon le nombre d'instance de *round*. Une architecture entièrement déroulée est présentée à la Figure 2. Le déroulage seul ne va pas augmenter la performance du circuit. Cependant, cela va permettre le pipelining.

- Pipelining externe : Le pipelining externe consiste à insérer des registres entre les blocs de l'architecture déroulée (entre les *rounds*). Cela augmente grandement les performances en terme de débit car des blocs de données différents peuvent maintenant être traités simultanément. Cela est aussi visible Figure 2.

<sup>1.</sup> *round* désigne l'ensemble des quatres opérations (*SubBytes*, *ShiftRows*, *MixColumns* et *AddRoundKey*) appliquées à l'*État* durant le (dé)chiffrement.

FIGURE 2: Architecture déroulée avec pipelining externe (source : [6])

- Pipelining interne : Pour réaliser du pipelining interne, des registres doivent être insérés à l'intérieur des blocs de chaque *round*. Cette architecture permet d'obtenir un débit encore plus élevé. Une architecture entièrement déroulée avec pipeline externe et interne est présenté Figure 3.

FIGURE 3: Architecture entièrement déroulée avec pipelining externe et interne (source :[6])

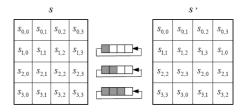

#### 2.1.2.2 Implémentations des différentes opérations

- SubByte: L'opération SubByte est originellement implémentée via une table de correspondance (Look Up Table). Cette table de correspondance peut être dans une RAM dédiée ou encore elle peut être générée par l'outil de synthèse à l'aide de portes combinatoires. On verra par la suite que les tables de correspondance, non optimisées pour une faible surface ou consommation, seront vite remplacées par d'autres solutions.

- ShiftRow: Cette opération consiste simplement en une réorganisation des bytes de l'État entre eux. Cela sera fait par un routage physique ou via un adressage adéquat de la mémoire stockant l'État.

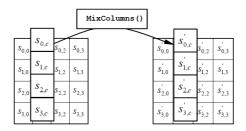

- MixColumns: L'opération MixColumns est implémentée à l'aide de portes combinatoires directement selon sa définition Equation A.3. Cependant, cette définition sera souvent réécrite pour obtenir un circuit plus compact.

- AddRoundKey: L'opération AddRoundKey consiste en une simple addition XOR.

- KeyScheduling<sup>2</sup>: La génération des clés succesives pour chaque round peut être vue de deux manières différentes. Soit les clés sont calculées à l'avance et stockées dans une mémoire à cet effet, soit celles-ci sont calculées au fur et à mesure en parallèle à l'exécution des rounds<sup>3</sup>. La première solution nécessitant une grande mémoire et donc une grande superficie et consommation, la deuxième approche sera utilisée pour les implémentations ciblant la faible consommation.

#### 2.1.3 Implémentation faible consommation

#### 2.1.3.1 S-Box

La S-Box, utilisée par l'opération *SubByte* et le *KeyScheduling*, étant la partie la plus coûteuse en terme de délai, superficie et consommation (75% de la consommation totale selon [14]), plusieurs auteurs se sont donc interessés uniquement à l'optimisation de celle-ci. La table de correspondance est sans doute la solution la plus simple à mettre en oeuvre mais présente deux inconvénients majeurs. Premièrement, elle utilise une grande superficie. Deuxièmement, le délai de la table de correspondance est bien souvent le facteur limitant d'une architecture avec pipeline interne car il s'agit du délai le plus important à l'intérieur d'un *round*. Dans le cadre d'une implémentation faible consommation, le pipelining ne sera pas souvent utilisé mais le délai de la S-Box restera tout de même le plus important, toutes architectures confondues, et déterminera donc en grande partie la fréquence de fonctionnement du circuit.

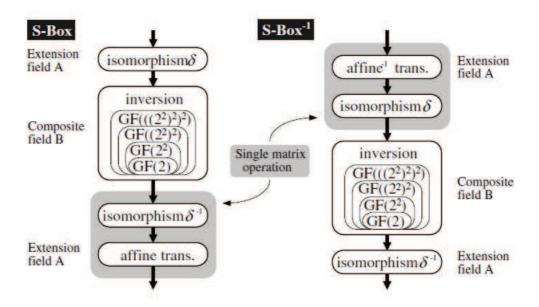

Une alternative à la table de correspondance est l'utilisation de la logique combinatoire seule grâce à la théorie des corps finis (corps de Galois). Cela a été suggéré pour la première fois par V. Rijmen, l'un des auteurs de l'AES, dans [7] mais sans aucune implémentation. A. Satoh *et al.* présentent une première implémentation dans [8]. La méthode est la suivante : les éléments du corps  $GF(2^8)$  (que sont les bytes) sont succesivement mappés vers des éléments des corps homomorphiques  $GF((2^4)^2)$  et ensuite  $GF(((2^2)^2)^2)$ , où les opérations sont éffectuées facilement à l'aide de logique combinatoire simple.

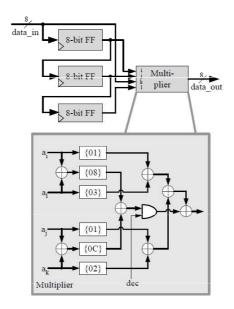

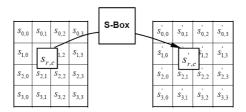

La S-Box peut être divisée en trois parties : d'abord une transformation du corps  $GF(2^8)$  vers le corps  $GF(((2^2)^2)^2)$ , ensuite une inversion dans le corps  $GF(((2^2)^2)^2)$  et enfin, la transformation inverse du corps  $GF(((2^2)^2)^2)$  vers le corps  $GF(2^8)$  combinée avec la transformation affine. Cela est représenté Figure 4. L'inversion dans le corps  $GF(((2^2)^2)^2)$  est visible Figure 5. Le corps  $GF(((2^2)^2)^2)$  est construit en appliquant de multiples extensions de degré 2 au corps GF(2). Chacune de ces extensions requiert un polynôme irréductible servant de base. Il y a plusieurs possibilités pour le choix de ces polynômes, et cela déterminera

<sup>2.</sup> KeyScheduling désigne le mécanisme fournissant les clés nécessaires à l'exécution de l'opération AddroundKey pour chaque round.

<sup>3.</sup> Dans la suite de ce travail, on désignera par on-the-fly cette deuxième méthode.

FIGURE 4: Structure de la S-Box de Satoh et al. (source : [8])

en partie la complexité du circuit. Ainsi, dans [8], les polynômes choisis sont :

$$\begin{cases}

GF(2^2) &: x^2 + x + 1 \\

GF((2^2)^2) &: x^2 + x + \emptyset \\

GF(((2^2)^2)^2) &: x^2 + x + \lambda,

\end{cases} \tag{2.1}$$

avec  $\phi = \{10\}$  and  $\lambda = \{1100\}$ . A partir de ces bases, il est possible de créer une matrice pour effectuer la transformation (isomorphisme) qui sera ensuite implémentée en logique combinatoire [18].

Le nombre de portes équivalentes obtenu pour la S-Box lors de la synthèse en technologie CMOS  $0.11\mu m$  est de 294 et le délai est de 3.69 ns (ou 286 portes équivalentes en technologie CMOS  $0.18\mu m$ , tel que calculé par Mentens dans [10], voir plus bas). Selon leur calcul, cela représente une taille 4 fois plus petite qu'avec une table de correspondance.

Wolkerstorfer *et al.* ont également réalisé dans [9] l'implémentation d'une S-Box en utilisant la théorie des corps finis. Cependant, ils se sont limités à représenter les éléments du corps  $GF(2^8)$  en une extension du corps  $GF(2^4)$ , comme proposé initialement par Rijmen dans [7]. Leur implémentation, qui combine la S-Box et la S-Box inverse (pour le processus de déchiffrement) contient 406 portes équivalentes pour une superficie de  $0.108 \text{mm}^2$  et une fréquence de 70MHz en technologie CMOS  $0.6 \ \mu\text{m}$  d'*AMS*. Pour une S-Box implémentée à l'aide d'une table de correspondance, ils obtiennent une superficie de  $0.200 \text{mm}^2$  avec la même technologie.

**FIGURE 5:** Inversion dans le corps  $GF(((2^2)^2)^2)$  (source : [8])

Macchetti *et al.* présentent dans [12] une autre implémentation basée sur la décomposition en sous-corps. Ils se limitent également à une décomposition dans  $GF(2^4)$  mais en utilisant une représentation comme décrite par Rudra *et al.* dans [13]. La synthèse de leur circuit en technologie CMOS  $0.25\mu$ m 1.8V de chez *STMicroelectronics* donne une superficie de 0.075mm<sup>2</sup> pour un délai de 7.94ns. Les auteurs donnent également ici des informations concernant la puissance. Ils ont synthétisé un circuit de *round* complet en utilisant leur S-Box. La consommation du circuit est de 2mW pour un délai de 12 ns. On peut remarquer ici que le délai de la S-Box intervient pour 66% du délai total.

Dans [10], Mentens *et al.* améliorent le travail de Satoh en étudiant de manière exhaustive le choix des polynômes de base. Ils montrent qu'un meilleur choix peut amener à une réduction de superficie de 5% par rapport à celui de Satoh. En particulier, en choisissant  $\lambda = \{1000\}$ , la S-Box contient maintenant 272 portes équivalentes pour une synhtèse en technologie CMOS  $0.18\mu m$ .

Dans [11], Canright va un cran plus loin en incluant les bases normales en plus des bases polynomiales lors du choix des bases pour les extensions. De plus, il choisit correctement les portes utilisées (en en remplaçant certaines par des NOR qui sont plus petites dans la bibliothèque CMOS  $0.13\mu$ m utilisée) et il utilise une meilleure méthode (algorithme de recherche par arbre) pour optimiser les isomorphismes obtenus (éliminer la redondance). Cela lui permet de diminuer la superficie de 20% par rapport à Satoh [8].

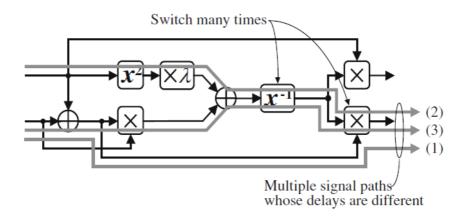

En 2003, Morioka et Satoh [14] présenteront pour la première fois une implémention de la S-Box optimisée spécifiquement en vue d'une faible consommation. Ils remarquent d'abord que la taille du circuit à moins d'effet que prévu sur la consommation. Particulièrement, ils montrent qu'une implémentation directe de la relation entrée-sortie via une structure type *somme des produits* consomme moins qu'une implémentation à l'aide des corps composés, pourtant de plus faible superficie. Cela est expliqué par des transitions non-désirées (1) à la suite des différences entre les temps d'arrivée des signaux à l'entrée d'un module

**FIGURE 6:** Différence entre les temps d'arrivée des signaux dans la structure présentée Figure 5 (source : [14])

(Figure 6) et (2) à l'utilisation de beaucoup de portes XOR qui ont une probabilité de propagation des transitions valant 1 au lieu de 0.5 pour les autres portes. L'implémentation de la S-Box qu'ils proposent est donc optimisée de manière à réduire ces transitions indésirables. Pour ce faire, ils se base sur la structure de décomposition en sous-corps finis déjà dévelopée par Satoh dans [8]. Ils divisent cette structure en trois étages, chacun implémenté via un réseau de type PPRM (Positive Polarity Reed-Muller). Les temps d'arrivée des signaux entre les étages sont égalisés par des chaînes de délai quand cela est nécessaire. Synthétisé en technologie CMOS  $0.13\mu$ m 1.5V, leur S-Box consomme  $29\mu$ W à une fréquence de 10MHz. Une version combinée des S-Box directe et inverse consomme en moyenne  $74.5\mu$ W pour un délai de 2ns et un nombre de portes de 725, toujours dans cette même technologie.

Un deuxième travail sur l'implémentaion faible consommation de la S-Box a été réalisé par Bertoni et Macchetti dans [15]. Leur contribution porte sur l'optimisation au niveau logique de la la fonction non-linéaire qu'est la S-Box. La méthode utilisée est la suivante : la S-Box, à N bits d'entrée et N bits de sortie, est vue comme une fonction de permutation sur un ensemble S, un isomorphisme. Si les éléments de S sont représentés par un codage de type one-hot, le nombre de bits d'entrée et de sortie va grandir à  $2^N$  mais l'isomorphisme sur S ne sera plus qu'un simple réarrangement des bits de l'entrée vers la sortie, donc ne consommant aucune puissance. Un décodeur placé à l'entrée permet de réaliser le codage one-hot (de N bits vers  $2^N$  bits) et un encodeur à la sortie permet de retrouver le codage initial à la sortie (de  $2^N$  bits vers N bits).

Par souci de confidentialité, les auteurs ne dévoilent pas leurs résultats absolus. Par contre, avec une synthèse en technologie CMOS 0.18µm 1.8V de chez *STMicroelectronics*, ils rapportent une réduction de puissance de 57% par rapport à une S-Box traditionelle implémentée comme une table de correspodance pour une augmentation de superficie de 11%, cela à une fréquence de 1GHz. Ils rapportent également un meilleur produit puissance-délai par

rapport aux autres implémentations précédement réalisées, y compris celle de Morioka et Satoh, mais sans donner de chiffres.

Tillich *et al.* ont réalisé en 2006 une comparaison des différentes S-Box existantes en terme de superficie, délai et puissance [16]. Pour ce faire, ils ont re-synthétisé les différentes S-Box en technologie CMOS 0.35µm de chez *AMS*. Les résultats sont :

- 1. la plus petite superficie est obtenue avec la S-Box de Canright [11] suivi de près par celle de Wolkerstorfer *et al.* [9] et celle de Satoh *et al.* [8]. Il s'agit des S-Box utilisant l'arithmétique des corps finis.

- 2. la plus faible puissance revient à la S-Box de Bertoni *et al.* [15]. Il est intérressant de remarquer que les S-Box qui consomment le plus sont celles de plus petite superficie sus-citées.

- 3. une dernière mesure reportée, fort utile dans le cas de circuits tels que les tags RFID, est le produit puissance-superficie. Les résultats sont les mêmes que ceux pour la puissance.

Il est à noter que la S-Box de Morioka *et al.* et celle de Mentes *et al.* ne faisaient pas partie de la comparaison.

Enfin, le travail le plus récent [17] révèle une autre approche. Alors que tous les précédents travaux présentent des optimisations au niveau logique, ici c'est au niveau du transistor que l'étude est faite. Reprenant la S-Box de Mentes  $et\ al$ . pour sa faible taille, les auteurs étudient l'évolution de la consommation de la S-Box en fonction de différents paramètres technologiques (tension de seuil et taille des transistors) et fonctionnels (fréquence et tension d'alimentation). Il y est expliqué comment le concepteur peut réduire la consommation du circuit en choissant de manière adéquate la technologie. Ainsi, avec une technologie CMOS 65nm 1.2V LP SVT, la consommation de la S-Box est réduite à 90nW à 100kHz. De plus, si la tension  $V_{dd}$  est réduite à 0.8V, une réduction de 60% supplémentaire est possible pour atteindre 37nW. Il est intérressant de remarquer que ces choix technologiques, proposés dans ce travail, modifient principalement la consommation statique du circuit et non la consommation dynamique, qui est la principale cible de tous les autres travaux.

Le lecteur interressé peut se référer à [18] pour plus de détails concernant l'arithmétique des corps finis et son application aux circuits logiques.

#### 2.1.3.2 Co-processeur AES complet

Les premières implémentations matérielles de l'algorithme *Rijndael* ont été faites durant la deuxième étape de sélection pour les différents candidats à l'AES. Ainsi, dans [19] l'algorithme Rijndael a été synthétisé dans une technologie CMOS 0.5µm propre à la *National*

Security Agency. Les résultats sont fournis pour une version itérative et une version avec pipeline externe intégral. Il s'agit d'une synthèse basique sans aucune optimisation spécifique. Les S-Box sont implémentées par des tables de correspondance. La version itérative du circuit présente une superficie de  $46 \text{ mm}^2$  ( $\sim 1000000 \text{ portes}$ ) et un débit de 443 Mbits/s. La version pipelinée a une superficie de  $471 \text{ mm}^2$  ( $\sim 7000000 \text{ portes}$ ) et un débit de 5.163 Gbits/s. Dans [20], la National Institute of Standards and Technology a fait le même travail en technologie CMOS  $0.35 \mu \text{m}$  de chez Mitsubishi Electric. Ici, il s'agit d'une architecture entièrement déroulée mais sans pipeline. Le circuit présente une superficie de 612000 portes et un débit de 1.95 Gbits/s.

Parmi les premiers à s'être attelés à l'optimisation du circuit, on peut citer le travail de Kuo *et al.* dans [21]. Partant du fait que l'algorithme est fortement symétrique comme le montre la Figure 7, les auteurs ont minimisé la superficie et le chemin critique par un design rigoureux. Pour balancer correctement performance et superficie, ils choisisent une architecture basique itérative. Un *round* est éxécuté en un cycle d'horloge. Aucun déroulement ni pipeline n'est utilisé. Les clefs succesives sont générées *on-the-fly*. Le chemin de données interne a une largeur de 256 bits. Seul le chiffrement est implémenté ici. Les choix pour

FIGURE 7: Symétrie dans l'algorithme de *Rijndael* (redessiné d'après [21])

l'implémentation des différentes opérations sont les suivants. Les S-Box, pour l'opération *SubByte*, sont implémentées via des tables de correspondances en logique combinatoire. Il y a 48 S-Box au total (32 pour un *round* et 16 pour le *KeyScheduling*). L'opération *ShiftRow* utilise également une table de correspondance pour déterminer l'étendue du décalage. L'opération *MixColumn* est implémentée directement d'après sa définition (Équation (A.3)). Enfin, l'opération *AddRoundKey* est une simple addition XOR. Le *KeyScheduling* est conçu de manière à pouvoir utiliser toute les combinaisons taille de bloc de données/taille de la clé

possible. La constante de *round* est également fournie via une table de correpondance. Synthétisé en technologie CMOS 0.18µm de chez *National Semiconductor* en condition normale (1.8V et 16°C) le circuit a une superficie de 3.96mm<sup>2</sup> (173000 portes) et présente un débit max de 1.83Gbits/s à 100MHz.

Ainsi, même si ce travail ne présente pas une implémentation faible superficie à proprement parler, cette première optimisation montre déjà une réduction notable de superficie comparée aux précédents résultats.

Dans [22], Lu *et al.* présentent un circuit adapté aux applications contraintes par la taille telles que les *smart card*, PDA ou encore téléphones mobiles. L'architecture est de type itérative. Le chemin de données est de 128 bits. Deux cycles sont requis par *round*. Un (dé)chiffrement nécéssite 21 cycles. Les auteurs proposent de réutiliser le maximum de matériel pour effectuer le chiffrement et le déchiffrement. Ainsi, chacun des modules servant à effectuer les quatres opérations ainsi que le *KeyScheduling* peuvent réaliser l'opération directe ou inverse choisi par un bit de sélection présent sur les modules.

La S-Box utilise une table de correspondance (commune au chiffrement et déchiffrement) pour calculer l'inverse tandis que la transformation affine est réalisée en combinatoire. L'opération *MixColumn* est obtenue en décomposant la matrice de l'Equation A.3 en deux matrices puis en factorisant les termes communs.

La synthèse en technologie CMOS  $0.25\mu$ m de chez TSMC produit un circuit de 32000 portes offrant un débit de 609Mbits/s à 100MHz. Ainsi, les auteurs rapportent qu'en partageant efficacement le matériel entre le chiffrement et le déchiffrement, la taille du circuit est réduite de 68% par rapport aux autres designs.

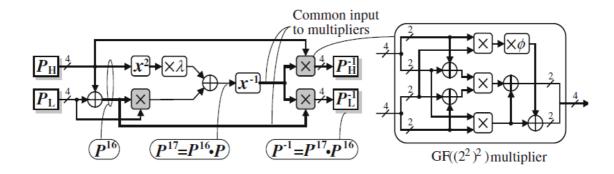

Grâce notamment à la S-Box entièrement combinatoire déjà présentée précédemment dans ce texte, Satoh *et al.* réduisent de manière significative la superficie du circuit dans [8]. L'architecture est ici aussi itérative. Le chemin de données est de 32 bits et le circuit dispose de quatre instances de la S-Box. Pour encore réduire la taille, ces quatres S-Box sont aussi utilisées pour le *KeyScheduling*, qui est réalisé *on-the-fly*. Ainsi, un *round* est réalisé en cinq coups d'horloge (pour une taille de bloc de données et de clé de 128 bits) et le chiffrement complet nécéssite 54 cycles  $(10 \times 5 + 4 \text{ cycles pour le premier } round \text{ dont la clé est directement disponible sans utiliser les S-Box). Enfin, le circuit permet le chiffrement et le déchiffrement.$

Les optimisations spécifiques aux opérations sont : *SubByte* est réalisée à l'aide de la S-Box déjà détaillée plus haut dans ce texte, *MixColumn* est optimisée de la même manière que dans [22] et enfin, le *KeyScheduling* utilise un générateur de constante de *round* évitant ainsi le recours à une table de correspondance.

Le circuit est synthétisé en technologie CMOS 0.11 $\mu$ m. La superficie obtenue est de 0.052mm<sup>2</sup> (5398 portes) et le débit est de 311Mbits/s à 131MHz. Une architecture 1 cycle/*round*, obtenue en augmentant la taille du chemin de données à 128 bits et en multipliant par quatre les instances de chaque bloc, a aussi été synthétisée. La superficie est mainteannt de 0.205mm<sup>2</sup>

(21337 portes) pour un débit de 2.6 Gbits/s à 224MHz.

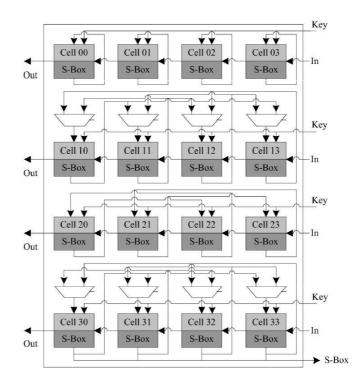

Reprochant au design de Satoh *et al.* d'avoir des chemins fortement non-balancés et possédant des fonctions de sélection qui gaspillent temps et superficie, Mangard *et al.* présentent une nouvelle approche dans [23]. Les clés du design sont : (1) des chemins balancés et courts, permettant d'utiliser efficacement chaque cycle et réduisant le risque de transitions non-désirées, ce qui est profitable pour un design basse consommation ; (2) une grande régularité dans l'architecture permettant un placement et routage plus efficace qui fournira un circuit plus compact ; (3) une architecture évolutive pouvant être mise à l'échelle facilement en fonction des besoins tels qu'une augmentation des performances au détriment de la taille, une utilisation de clé de 128, 192 ou 256 bits.

L'unité de données est présentée Figure 8. Chaque cellule comprend un registre 8 bits ainsi que de la logique combinatoire pour effectuer certaines opérations. Contrairement aux autres circuits qui stockent l'*Etat* en cours dans un registre de 128 bits unique, ici l'*Etat* est stocké dans 16 registres de 8bits. Les différentes opérations sont idéalement implémentées grâce à cette disposition en faisant transiter les données d'une cellule à l'autre. Toutes les opérations, à l'exception de *SubByte*, sont réalisées à l'intérieur des cellules.

FIGURE 8: Architecture très régulière de Mangard et al. (source : [23])

La S-Box est une implémentation pipelinée à deux étages (afin de balancer correctement les chemins) de la version de Wolkerstorfer *et al.* [9]. Une version haute performance de l'architecture est également présentée et contient seize S-Box (une par cellule) au lieu de quatre.

Cette version permet d'éxécuter un *round* en trois cycles au lieu de six pour la version standard. Le *KeyScheduling* calcule les clés *on-the-fly* et utilise les S-Box de l'unité de données. Les deux versions sont synthétisées en technologie CMOS 0.6µm. La version standard contient 10800 portes et présente un débit de 128Mbits/s. La version haute performance contient 15500 portes et offre un débit de 241 MBits/s. Tous deux fonctionnent à 64MHz. En utilisant la même technologie CMOS que Satoh *et al.*, les auteurs estiment une fréquence de fonctionnement trois fois supérieure à la leur.

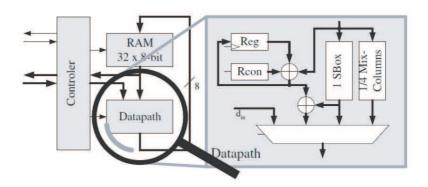

Alors que certaines implémentations sur circuits logiques programmables ont déjà été optimisées pour réduire la superficie, tel le travail de F.-X. Standaert *et al.* [24], la première implémentation spécialement optimisée basse consommation sur circuit intégré spécifique, en vue d'une utilisation sur tag RFID, est présentée par Feldhofer *et al.* dans [25]. Compte tenu de l'application, ils estiment qu'un courant de 15µA est disponible pour le circuit AES, qui ne devrait pas dépasser 5000 portes en superficie. De plus, le protocole utilisé pose une contrainte temporelle de 18ms pour le chiffrement d'un bloc de 128 bits de données. Les auteurs rapportent qu'aucun circuit jusqu'à présent ne peut respecter de telles contraintes.

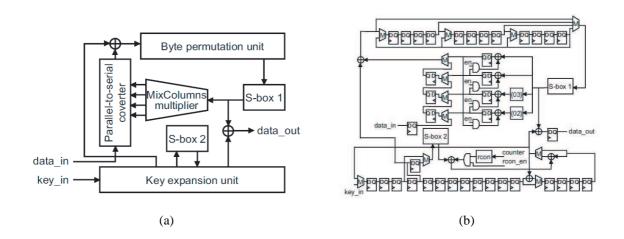

**FIGURE 9:** Architecture 8 bits proposée par Feldhofer *et al.* (source : [25])

L'architecture proposée, telle que présentée Figure 9, est une architecture itérative avec chemin de données de 8 bits. Cela permet de réduire fortement la consommation comparé aux architectures 128 bits ou même 32 bits. Le module contient une mémoire RAM de 256 bits pour stocker l'*État* ainsi que la *round key*, le chemin de données et une unité de contrôle implémentée par une machine à états. Le chemin de données contient de la logique combinatoire ainsi que des modules pour réaliser les opérations. L'opération *MixColumn* est effectuée byte par byte par un module. L'opération s'effectuant sur une colonne, celui-ci contient trois registres de 8 bits pour stocker temporairement les bytes de la colonne en cours. La S-Box est à nouveau une implémentation pipelinée à deux étages de la version de Wolkerstorfer *et al.* [9]. Seule une instance de la S-Box est présente dans le circuit pour minimiser la superficie. Un chiffrement complet nécessite 1016 cycles d'horloge. Synthétisé en technologie CMOS 0.35µm, la superficie du circuit est de 3595 portes. Une fréquence de 100kHz permet de respecter la contrainte temporelle. Enfin, la consommation du circuit est de 8.15µA.

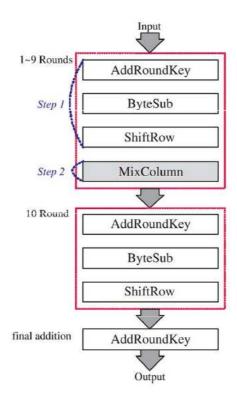

La deuxième réalisation basse consommation, toujours pour application de type tag RFID, est proposée par Kim *et al.* dans [27]. Reprenant une architecture semblable à celle de Feldhofer *et al.* [25] (itérative, 8 bits), les auteurs proposent ici une optimisation au niveau fonctionnel en réorganisant et regroupant les opérations de l'algorithme comme indiqué sur la Figure 10. Ainsi, un *round* principal est éxécuté en deux étapes fonctionnelles, au lieu de trois dans [25]. La mémoire pour l'*État* et la clé est scindée en deux pour permettre un accès

**FIGURE 10:** Réorganisation des *rounds* par Kim *et al.* (source : [27])

en parallèle. La S-Box est encore une implémentation de la S-Box présentée par Wolkerstofer *et al.* dans [9]. L'opération *MixColumn* se fait également byte par byte de la même manière que dans [25] à la différence près que le module contient ici un registre de 32 bits. Le circuit est synthétisé dans deux technologies CMOS  $0.25\mu m$  2.5V de chez *Hynix Corp.* et de chez *Samsung Electronics*. L'architecture proposée nécéssite 870 cycles d'horloge pour chiffrer 128 bits de données. Le circuit compte respectivement 3900 et 3868 portes pour les technologies *Hynix* et *Samsung*. Fonctionnant à 100kHz, la consommation est de  $4.85\mu W$  (ou  $1.94\mu A$ ) et  $21.4\mu W$  (ou  $8.56\mu A$ ).

Dans [28], Feldhofer *et al.* présentent une version améliorée de leur précédente réalisation [25]. Le circuit permet maintenant de chiffrer ou déchiffrer les données. L'architecture est presque identique à celle de [25]. Un module d'entrée/sortie est rajouté pour permettre d'utiliser le circuit comme un coprocesseur. Le clock gating est rigoureusement appliqué à

toutes les cellules séquentielles du circuit. Lorsque la S-Box n'est pas utilisée, son entrée est isolée et une valeur de  $\{0x52\}$  y est appliquée pour annuler la sortie. Les opérations MixColumn et InvMixColumn sont intégrées dans un même module. D'après les équations :

$$c(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$$

$$c^{-1}(x) = \{0b\}x^3 + \{0d\}x^2 + \{09\}x + \{0e\}$$

$$c^{-1}(x) - c(x) = \{08\}x^3 + \{0c\}x^2 + \{08\}x + \{0c\}$$

$$c^{-1}(x) - c(x) = \{08\}(x^3 + x) + \{0c\}(x^2 + 1)$$

$$c^{-1}(x) = c(x) + \{08\}(x^3 + x) + \{0c\}(x^2 + 1)$$

les auteurs remarquent que l'opération inverse est facilement obtenue à partir de l'opération directe et que du matériel peut être économisé en intégrant les deux opérations dans le même module comme le montre leur implémentation à la Figure 11.

FIGURE 11: Module réalisant les opérations *Inv/MixColumn* (source : [28])

Le circuit est synthétisé et réalisé en technologie CMOS  $0.35\mu m$  de chez *Philips Semiconductors*. Le chip fonctionnel obtenu comporte 4400 portes pour une superficie de  $0.25 mm^2$ . La consommation du circuit est directement mesurée sur le chip. A 100 kHz et avec une tension d'alimentation de 1.5 V, le courant est de  $3\mu A$ . Les auteurs reportent que le circuit est fonctionnel jusqu'à une tension minimum de 0.65 V.

Enfin, une dernière implémentation basse consommation est réalisée par Hämäläinen *et al.* dans [30]. Encore une fois, la taille du chemin de données est de 8 bits. Mais une toute autre approche concernant l'architecture est montrée ici. A la différence des autres travaux

[25], [27] et [28] qui réalisent les différentes opérations séquentiellement via une machine à états, les opérations sont exécutées en parallèle.

FIGURE 12: (a) Diagramme haut-niveau, (b) Chemin de données (source : [30])

La Figure 12 présente le diagramme haut-niveau en (a) et l'implémentation de celui-ci en (b). Chacunes des opérations possèdent leur propre module qui sont disposés les uns à la suite des autres. Avec une telle architecture, la S-Box du chemin de données principal est continuellement utilisée. Dès lors, une deuxième S-Box est présente sur le circuit pour éviter de devoir arrêter l'exécution des *round* lors du calcul des clés par le *KeyScheduling*. Etant implémentée selon le design très compact de Canright [11], cette S-Box supplémentaire n'augmente pas de beaucoup la taille du circuit. Ce design permet de réaliser le chiffrement en 160 cycles d'horloge.

Le circuit est synthétisé en technologie CMOS  $0.13\mu m$  1.2V. En optimisant la synthèse pour la plus faible consommation, le circuit comporte 3200 portes et consomme  $13\mu W/MHz$ . La fréquence maximum est de 130MHz ce qui permet un débit de 104Mbits/s.

On retiendra de ces travaux qu'ils ont tous été réalisés avec une technologie CMOS supérieure à  $0.11\mu m$  et qu'aucun n'utilise la logique sous-seuil, pourtant très efficace pour réduire la consommation comme le présente la section suivante. Aussi, si la réduction de la consommation est souhaitée à tout prix, on privilégiera une architecture avec chemin de données étroit (8 bits) et de type itérative, au détriment des performances.

#### 2.2 Logique sous-seuil

#### 2.2.1 Introduction

Etant donné l'étendue des recherches dans le domaine de la logique sous-seuil, il sera bien difficile ici d'être exhaustif. Cependant, un certain nombre de publications récentes présentant des circuits à très faible consommation grâce à une tension d'alimentation  $V_{dd}$  sous la tension de seuil  $V_t$  seront exposées ici. Cela permettra de décrire les différentes techniques utilisées dans la logique sous-seuil mais aussi de mettre en évidence le gain non négligeable de consommation apporté. Mais voyons d'abord pourquoi la logique sous-seuil est intéressante lorsqu'une faible consommation est requise.

L'énergie disipée par une porte logique peut être divisée en deux catégories : énergie statique et énergie dynamique. Le premier terme correspond à l'énergie consommée lorsque la porte est au repos. Cette dissipation est dûe uniquement aux différents courants de fuite. Le second terme correspond à l'énergie dissipée lorsque qu'un noeud est chargé ou déchargé. Les expressions de ces deux termes peuvent s'écrire comme :

$$E_{dyn} \propto C_{eff} V_{dd}^2 \tag{2.2}$$

$$E_{stat} = \frac{I_{leak}V_{dd}}{f_{clk}} \tag{2.3}$$

avec  $C_{eff}$  la charge effective de la porte (contenant  $C_L$ , la capacité de charge du noeud, ainsi que des facteurs tenant compte des courants de court-circuit et du facteur d'activité),  $f_{clk}$  la fréquence d'horloge et  $I_{leak}$  les courants de fuite.

Lorsque que l'on réduit la tension d'alimentation  $V_{dd}$ , on observe que les deux composantes de l'énergie telles que décrites ci-dessus vont être diminuées, comme le suggère les Équations (2.2) et (2.3). Cependant, cette diminution de tension a d'autres conséquences sur le circuit logique. En effet, en observant l'expression du délai d'une porte :

$$T_{del} \propto \frac{C_L V_{dd}}{I_{cr}},$$

(2.4)

$I_{on}$  étant le courant actif qui croît exponentiellement avec  $V_{dd}$  en régime sous-seuil, on remarque que cette diminution de tension va faire augmenter le délai de manière significative. Cette augmentation de délai, qui correspond à une réduction de la fréquence, pourra être acceptable pour les applications demandant de faibles ou moyennes performances. Par contre, un deuxième regard à l'Équation (2.3) nous indique que cette réduction de fréquence va à son tour conduire à une augmentation de l'énergie statique et qui sera malheureusement bien plus importante que la réduction provoquée par la diminuton de  $V_{dd}$ . Ainsi, on comprend que d'une part la réduction de l'énergie dynamique et d'autre part l'augmentation de l'énergie statique donnera lieu à un point d'énergie minimum. Ce point d'énergie minimum n'est pas une constante mais varie en fonction de la technologie utilisée [43], des caractéristiques du

circuit et des conditions de fonctionnement [32]. Il est possible de le calculer en additionnant les deux composantes de l'énergie et en calculant la dérivée par rapport à  $V_{dd}$ . Le développement est fait dans [31] et [32]. Les résultats montrent que la tension  $V_{dd}$  correspondant à ce point d'énergie minimum,  $V_{min}$ , ne dépend pas de  $V_t$  et se situe dans la région  $V_{dd} < V_t$ . Cela s'explique par le fait que, dans la région sous-seuil, le période pendant laquelle le circuit "fuit" (délai) croît exponentiellement alors que les courants de fuite ne sont pas réduits aussi rapidement lorsque que  $V_{dd}$  diminue.

Ainsi, on voit l'interêt de la logique sous-seuil lorsqu'il s'agit de concevoir des circuits à (très) faible consommation. La fin de ce chapitre présente les techniques utilisées en logique sous-seuil et les résultats de quelques circuits récents opérant à une tension  $V_{dd}$  située sous la tension de seuil  $V_t$  et affichant des consommations très faibles.

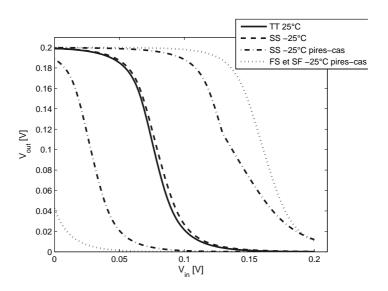

#### 2.2.2 Bibliothèque de cellules

Lors de la synthèse de circuits en régime sous-seuil à l'aide de bibliothèques de cellules standards, une sélection et/ou modification de celles-ci est nécessaire. En effet, lorsque que la tension d'alimentation devient trop faible, les cellules peuvent ne plus fonctionner correctement. Considérons le cas d'un inverseur. Celui-ci fonctionnera correctement que si son rapport  $I_{on}/I_{off}$  est suffisament grand. Ce rapport est fortement réduit en régime sous-seuil dû à la dépendance exponentielle de  $I_{on}$  avec  $V_{dd}$ . Dès lors, en considérant les variations technologiques (corners FS et SF  $^4$ ), il est calculé dans [33] que, pour un inverseur en technologie  $0.18\mu m$ , la tension de fonctionnement minimum,  $V_{dd,limit}$ , est de 195 mV, lorsque qu'il est idéalement dimensionné. Pour les dimensions standards de la bibliothèque, la tension minimum est de 220 mV. Cependant, cette tension minimum de fonctionnement,  $V_{dd,limit}$ , sera en général, pour les cellules simples, inférieure à la tension correspondant au point d'énergie minimum,  $V_{min}$ .

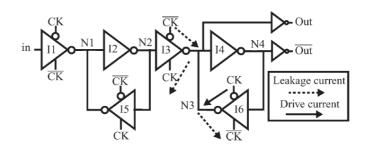

Il en va autrement pour des cellules plus complexes ou des cellules séquentielles. La Figure 13 montre le cas d'un flip-flop en technologie  $0.18\mu m$  [32]. Les inverseurs sont tous de tailles égales et minimales, sauf  $I_3$  qui est plus grand, diminuant ainsi  $t_{clk\to Q}$ . Lorsque la tension est diminuée, le PMOS de  $I_6$  ne parvient pas à garder le noeud  $N_3$  à l'état haut à cause des courants de fuite des NMOS de  $I_6$  et  $I_3$  qui sont trop importants. Une réduction de la taille de  $I_3$  et une augmentation de  $I_6$  est nécéssaire pour pouvoir utiliser ce flip-flop jusqu'à une tension de 300mV.

Un autre exemple est donné dans [39] pour un multiplexeur. Les auteurs proposent de transformer un multiplexeur 4:1 *one-hot* en un multiplexeur 4:1 *encodé* à l'aide de multiplexeurs 2:1 de manière à réduire les transistors "fuiants" en parallèle. Cette méthode permet d'obtenir une tension du niveau logique de sortie diminuée de 10% au lieu de presque 30% par rapport  $V_{dd}$  lorsque  $V_{dd} = 200$ mV.

<sup>4.</sup> F pour Fast, S pour Slow; la première lettre se rapportant au NMOS, la deuxième au PMOS.

FIGURE 13: Flip-flop (source : [32])

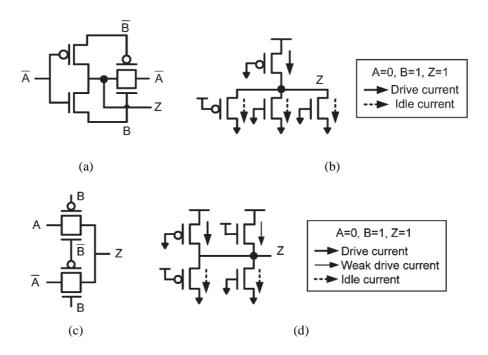

Plus généralement, plusieurs structures sont à éviter. Les cellules comportant des transistors en parallèle auront un rapport  $I_{on}/I_{off}$  réduit à faible tension. En effet, les courants de fuite des transistors en parallèle vont être aussi importants que le courant actif. La Figure 14 montre une porte XOR standard (a) (technologie  $0.18\mu m$ ) ainsi que les fuites dans les transistors en parallèle lorsque l'entrée A est basse et l'entrée B est haute (b). Alimentée à 100 mV, la tension de sortie ne sera que de 55 mV dans ce cas là, ce qui rend la cellule inutilisable [33].

**FIGURE 14:** (a) Porte XOR standard, (b) Fuites dans les transistors en parallèle quand {A=0, B=1}, (c) Porte XOR avec transistors de transmission, (d) Courants actifs et courants de fuite balancés (source : [33])

Une solution consiste à balancer correctement les courants de fuite avec les courants actifs par l'utilisation de transistors de transmission, comme sur la Figure 14 (c) et (d). Dans ce cas là, la porte est fonctionnelle à 100mV.

Les cellules comportant des transistors en série sont aussi à éviter. Cela à pour effet de réduire le courant actif. La tension de seuil des transistors empilés va aussi être augmentée, réduisant encore plus les courants actifs.

Dans tous les cas, la clé des designs en régime sous-seuil proposés jusqu'ici consiste à réduire la tension d'alimentation  $V_{dd}$  au point d'énergie minimum. Par ailleurs, quand le facteur de mérite important est la puissance instantannée, le concepteur veillera à rapprocher  $V_{min}$  au plus près de  $V_{dd,limit}$ , pour obtenir le circuit le plus efficace qu'il soit en terme de puissance [34].

#### 2.2.3 Variabilité

Les circuits logiques sont soumis à différentes variations. Il peut s'agir de variations globales opérationnelles ( $V_{dd}$ , température), de variations globales au niveau du process (longueur de grille, épaisseur d'oxide) ou encore de variations aléatoires comme la fluctuation du dopage dans le canal. Un effet important de ces variations va être de modifier  $V_t$ . Or, en régime sous-seuil, les portes logiques sont soumises à une sensibilité exponentielle à  $V_t$ . Dès lors, des disfonctionnements peuvent apparaître. Ceux-ci sont classés en deux catégories. On parle de disfonctionnement fonctionnel [35](la porte n'est plus capable de charger sa sortie à la tension d'alimentation) et de disfonctionnement paramétrique (violation de contrainte temporelle) [36] [38].

Lors de la conception d'un circuit, il est donc important de tenir compte des variations globales en prenant certaines marges pour s'assurer ainsi que le circuit reste 100% fonctionnel. Malheureusement, cela va écarter le circuit de son point de fonctionnement minimisant l'énergie. Différentes solutions ont donc été étudiées pour palier à ce problème. Une de ces solutions est le *body biasing*, qui consiste à appliquer une tension  $V_b$  au substrat du circuit et qui aura pour effet de modifier  $V_t$ . Ainsi, le courant  $I_{on}$  et donc le délai sont controlés. Cette tension peut être auto-régulée, comme dans [40].

Une autre solution consiste à faire varier  $V_{dd}$  –  $voltage\ scaling$  – qui, de la même manière que  $V_t$ , va permettre de contrôler  $I_{on}$  et donc le délai du circuit. Dans [37], une boucle de régulation de  $V_{dd}$  est proposée pour un filtre FIR en technologie CMOS 65nm. Le système permet d'adapter la tension d'alimentation comprise entre 0.25V et 0.7V ainsi que la fréquence en fonction de la charge du circuit. La méthode permet d'obtenir une réduction d'énergie de l'ordre de 50 à 100 %.

Une comparaison de ces deux techniques est faite dans [44]. Il en ressort que le *body* biasing est plus efficace que le voltage scaling car il donne lieu à un  $E_{min}$  plus faible.

#### 2.2.4 Résultats récents

Kaul *et al.* [39] présentent un accélerateur d'estimation de mouvement en technologie CMOS 65nm. En plus d'une architecture spécialement étudiée pour un fonctionnement à basse tension, les auteurs proposent un ajustement de la tension d'alimentation de  $\pm$ 0mV. Cette compensation permet d'annuler les effets des variations de température et de process lorsque le circuit travaille à une tension de 320mV. A la tension nominale de 1.2V, le circuit consomme 48mW pour une fréquence de 2GHz. Lorsque qu'il est utilisé en région sous-seuil à une tension de 320mV, qui représente le point d'énergie minimum, la consommation chute à  $56\mu$ W et la fréquence à 23MHz. Cette consommation peut encore être diminuée jusqu'à  $14.4\mu$ W en diminuant la tension à 230mV et qui permet d'utiliser le circuit à une fréquence de 4.3MHz.

Pu *et al.* présentent dans [41] un coprocesseur JPEG en technologie CMOS 65nm. Pour balancer correctement la tension de seuil des PMOS et NMOS du circuit soumise à des fluctuations dûes aux différentes variations (telles que décrites plus haut), ils utilisent un système de *body biasing* qui applique une tension à l'un des deux *well* du chip. La tension appliquée est auto-régulée via un petit module mesurant la différence de  $V_t$  des deux types de transistors. A la tension nominale de 1.2V, le circuit présente une consommation energétique de 7.5pJ/opération. Cette consommation est réduite à 0.9pJ/opération lorsque le circuit travaille en régime sous-seuil à une tension de 0.4V.

Un deuxième circuit proposé par Kaul et~al. utilise la logique sous-seuil [42]. Il s'agit ici d'un accélérateur de traitement vectoriel quadrivoie à double alimentation reconfigurable. Les techniques utilisées pour réduire la consommation sont (1) une double alimentation qui, en alimentant les parties du circuit les plus rapides avec la tension la plus basse, permet de réduire la consommation tout en gardant la même fréquence et (2) le *power gating* qui déconnecte de l'alimentation les parties du circuit non-utilisées. La consommation du circuit est de 161mW à 1.1V à une fréquence de 2.3GHz. En régime sous-seuil, la consommation chute à  $87\mu$ W à 230mV pour une fréquence de 8.8MHz. L'efficacité énergétique maximale est obtenue à 300mV avec 494GOPS/W.

Pour terminer cette section, il est intéressant de se demander ce que devient le comportement en régime sous-seuil des circuits pour les technologies plus avancées. Le travail de D. Bol *et al.* [46] étudie les performances en régime sous-seuil de circuits, du noeud technologique  $0.25\mu$ m jusqu'au noeud 32nm. Une évolution vers les noeuds plus avancés permet de réduire grandement la consommation dynamique grâce à la réduction de la capacité  $C_L$  ainsi que de la largeur de grille. Par contre, la consommation statique va augmenter à partir du noeud 180nm principalement à cause de la variabilité. La conclusion est que les noeuds

65/45nm en technologie LP<sup>5</sup> sont les plus intéressants pour la logique sous-seuil.

Ainsi, on voit que la logique sous-seuil permet de réduire de plusieurs ordres de grandeur la consommation des circuits. Cela se fait évidemment avec une nette diminution des performances. Cependant, pour les circuits ayant besoin d'une très faible consommation et dont les contraintes temporelles sont relativement lâches, les performances obtenues en régime sous-seuil sont encore acceptables. Enfin, il apparait que la technologie 65nm LP semble apporter le compromis idéal entre consommation dynamique et statique en régime sous-seuil.

#### 2.3 Conclusion

À la lumière de ce chapitre, on apperçoit une partie des motivations de ce travail. La première section nous a permis de remarquer que les coprocesseurs AES proposés jusqu'à maintenant n'utilisent pas la logique sous-seuil. De plus, les technologies utilisées dans ces travaux ne sont en général pas les plus avancées. La deuxième section nous a montrer que la logique sous-seuil se présente comme une solution idéale pour réduire la consommation des circuits. Aussi, une technologie plus avancée, telle la technologie 65nm LP, est plus adaptée, en terme d'efficacité énergétique, à la conception de circuits fonctionnants en régime sous-seuil.

Alors que la plupart des coprocesseurs AES réalisés jusqu'à présent souffrent d'une consommation encore fort élevée pour être utilisés sur des tags RFID, la logique sous-seuil semble bien adaptée à de tels circuits. Ce type de circuits ne présente pas de contrainte stricte sur la vitesse de fonctionnement mais est par contre très limité concernant sa consommation. En effet, le volume d'information échangé par les tags RFID est en général assez faible et le temps imparti pour l'échange peut s'élever à plusieurs centaines de millisecondes. D'un autre coté, l'alimentation de ces circuits donne une borne maximale pour la consommation énergétique (dans le cas d'une alimentation par batteries) ou pour la puissance (dans le cas d'une alimentation par champ électro-magnétique). L'utilisation d'un coprocesseur AES pour tag RFID en régime sous-seuil semble donc approprié pour réduire au maximum sa consommation. Ainsi, c'est à juste titre que ce travail propose cette étude.

<sup>5.</sup> pour *Low Power*. Cette technologie apporte une augmentation de la longeur de grille, de l'épaisseur de l'oxyde de grille et du dopage du canal en vue de diminuer les courants de fuite.

## Caractérisation des cellules

Les bibliothèques de cellules sont indispensables à la conception de circuits digitaux. Comme les fondeurs fournissent leurs bibliothèques uniquement caractérisées à la tension nominale, la conception et l'optimisation de circuits en logique sous-seuil n'est pas possible. En effet, sans ces bibliothèques caractérisées à basse tension, le comportement d'un circuit en régime sous-seuil ne peut être que mesuré, une fois le circuit réalisé à l'aide des bibliothèques caractérisées à la tension nominale. Dès lors, il apparait indispensable de posséder des bibliothèques caractérisées à basse tension pour pouvoir prédire le comportement du circuit et surtout pouvoir l'optimiser. Cette section étudie l'évolution des cellules lorsque  $V_{\rm dd}$  diminue en vue de caractériser une bibliothèque à basse tension. La première section propose une introduction aux bibliothèques digitales et à leur contenu. Ensuite, l'étude d'un inverseur lorsque  $V_{\rm dd}$  diminue est présentée au niveau du délai et de la consommation. Le problème de la variabilité est également abordé. Enfin, la méthode de caractérisation est présentée.

### 3.1 Introduction aux bibliothèques digitales

Le flot de design d'un circuit intégré digital nécessite l'utilisation de bibliothèques de cellules digitales. Ces bibliothèques contiennent, pour chacune des cellules, la description complète de celles-ci. Principalement, il y est décrit : les délais de propagation, les contraintes (pour les cellules séquentielles), les temps de montée/descente en sortie, la puissance de fuite pour chaque vecteur d'entrée, la puissance interne pour chaque transition ainsi que les capacités de chaque entrée. Tout ceci est détaillé dans cette section. La caractérisation d'une cellule consiste à obtenir les valeurs de ces différents paramètres. Ensuite, ces bibliothèques seront utilisées principalement pour synthétiser le circuit et pour vérifier la consommation de celui-ci. Il est donc essentiel de travailler avec une bibliothèque correctement caractérisée au niveau des délais pour être sûr de respecter la contrainte temporelle imposée au circuit. Notons que la caractérisation de la consommation des cellules est en général moins critique car cela n'influence pas la synthèse du circuit. La suite de cette section décrit brièvement la manière dont les délais et consommations sont modélisés au sein des bibliothèques.

#### 3.1.1 Délai dans la bibliothèque

Différents modèles peuvent être utilisés pour décrire le comportement temporel des cellules. Le plus courant est le modèle non-linéaire. Dans ce modèle, le délai total, de l'entrée d'une porte à l'entrée de la porte suivante est :

$$D_{total} = D_{propagation} + D_{connexion}, (3.1)$$

avec  $D_{propagation}$ , le délai de propagation de la cellule, définit comme le délai entre l'instant où  $V_{in}$ =0.4 $V_{dd}$  et le point  $V_{out}$ =0.6 $V_{dd}$  (pour une transition descendante à la sortie, et inversément pour un transition montante) et  $D_{connexion}$  qui représente le délai dû aux interconnexions entre la sortie de la porte et l'entrée de la porte suivante. Ces deux composantes se calculent comme suit :

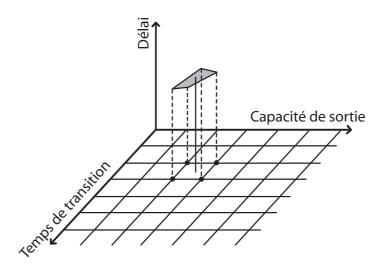

D<sub>propagation</sub> Le délai de propagation est obtenu à l'aide d'une recherche dans une table de correspondance indexée par le temps de transition à l'entrée et par la capacité de sortie. Pour obtenir une valeur particulière, une interpolation est réalisée sur les quatre points les plus proches (voir Figure 15).

$D_{connexion}$  Le délai de la connexion se calcule comme un délai de type RC en considérant que le réseau est balancé (les ports d'entrée se partagent la résistance et la capacité du fil à part égale) et vaut :

$$D_{connection} = \frac{R_{net}}{N} \left( \frac{C_{net}}{N} + C_{port} \right), \tag{3.2}$$

avec  $R_{net}$  la résistance totale et  $C_{net}$  la capacité totale d'interconnexion,  $C_{port}$  la capacité d'entrée de la porte suivante et N le fan-out.

Ainsi, pour pouvoir calculer les délais d'un circuit logique, les bibliothèques contiennent :

- des tables de correspondance indexées par le temps de transition à l'entrée et par la capacité de sortie pour les délais de cellule des transitions montantes et descendantes,

- des tables de correspondance indexées par le temps de transition à l'entrée et la capacité de sortie pour les temps de transition à la sortie,

<sup>1.</sup> Les seuils de  $0.4V_{dd}$  et  $0.6V_{dd}$  sont ceux utilisés par *STMicroelectronics* dans leurs bibliothèques et nous avons donc gardé cette convention. En général, un seuil unique de  $0.5V_{dd}$  à l'entrée et à la sortie est courament utilisé.

**FIGURE 15:** Table de correspondance pour le calcul du délai, indexée par le temps de transition à l'entrée et la capacité de sortie

- des modèles d'interconnexion (avec  $R_{net}$  et  $C_{net}$  en fonction de la longueur de l'interconnexion),

- les valeurs des capacités des ports d'entrée des cellules.

#### 3.1.2 Puissance dans la bibliothèque

L'équation modélisant la puissance dissipée dans une cellule est la suivante :

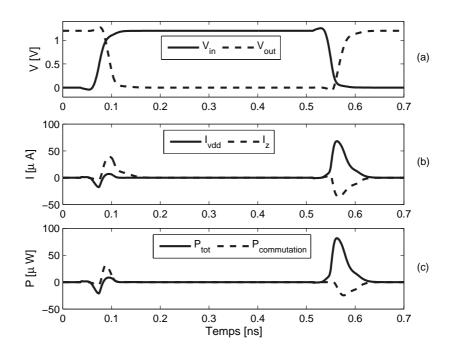

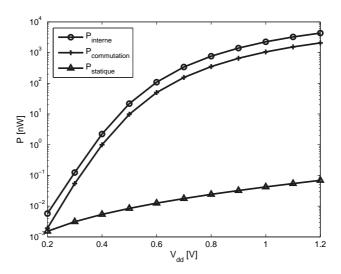

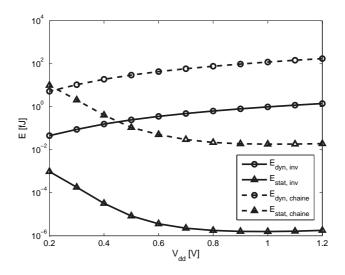

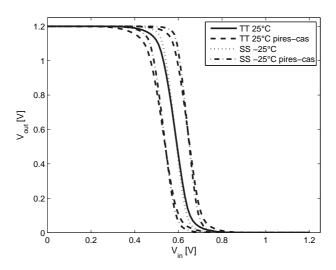

$$P_{total} = P_{statique} + P_{dynamique}, (3.3)$$