### Digital access to libraries

#### "Neuromorphic CMOS imager for sparse vision data acquisition"

Rousseau, Naomi

#### Abstract

The recent interest in modelling the human retina opens the doors to neuromorphic imagers. Neuromorphic engineering succeeds in achieving a biomimetic retina by providing an electrical model as close as possible to neuron architectures involved in the vision process: the event-based dynamic vision sensor (DVS) is designed for low-data and low-power image sensing acquisition. Its particularity resides in asynchronous pixels responding only to relative changes in light intensity. These sensors show a wide dynamic range, low power consumption and good time resolution. The visual neuromorphic field is thus not only promising for robotics, but also for real-time tracking. Dynamic vision sensors seem suitable for detecting sparse data acquisition but raise one question: how to efficiently decrease the power consumption of an asynchronous pixel responding only to relative changes in light intensity? Inspired from a state-of-the-art image sensor, this study proposes a new DVS design in a mat...

Document type: Mémoire (Thesis)

### Référence bibliographique

Rousseau, Naomi. *Neuromorphic CMOS imager for sparse vision data acquisition.* Ecole polytechnique de Louvain, Université catholique de Louvain, 2017. Prom. : Bol, David ; Flandre, Denis.

Available at:

http://hdl.handle.net/2078.1/thesis:10624

École polytechnique de Louvain (EPL)

# Neuromorphic CMOS imager for sparse vision data acquisition

Dissertation presented by **Naomi Rousseau**

for obtaining the Master's degree in **Electrical Engineering**

Supervisor(s) **David Bol, Denis Flandre**

Reader(s)

Charlotte Frenkel, Jean-Didier Legat

Academic year 2016-2017

## TABLE OF CONTENTS

|          | Ackr | nowledge  | ement                              | V         |

|----------|------|-----------|------------------------------------|-----------|

|          | Abst | ract .    |                                    | vii       |

|          | List | of Figur  | es                                 | ix        |

|          | List | of Table  | S                                  | xi        |

|          | List | of Acror  | nyms                               | xiii      |

| _        |      |           |                                    |           |

| In       |      | iction    |                                    | 1         |

|          | Targ | ets, cont | tributions and outline             | 2         |

| 1        | Fun  | dament    | cals and state of the art          | 3         |

|          | 1.1  | Human     | Retina                             | 4         |

|          |      | 1.1.1     | Architecture                       | 4         |

|          |      | 1.1.2     | Characteristics                    | 4         |

|          | 1.2  | Photod    | liode                              | 5         |

|          |      | 1.2.1     | Principles of operation            | 5         |

|          |      | 1.2.2     | Figures of merit                   | 7         |

|          | 1.3  | Addres    | ss-Event Representation            | 8         |

|          | 1.4  |           | us neuromorphic CMOS image sensors | 10        |

|          |      | 1.4.1     | Synchronous architectures          | 11        |

|          |      | 1.4.2     | Asynchronous architectures         | 12        |

|          |      | 1.4.3     | Summary                            | 16        |

| <b>2</b> | Pixe | el archi  | tecture and specifications         | 19        |

| _        | 2.1  |           | rchitecture                        | 20        |

|          | 2.2  |           | oles of operation                  | 21        |

|          | 2.3  | _         | eceptor circuit                    | 22        |

|          |      | 2.3.1     | Photodiode                         | 22        |

|          |      | 2.3.2     | Photoreceptor transistor           | 26        |

|          |      | 2.3.3     | Bias point                         | 26        |

|          | 2.4  |           | ed capacitor amplifier             | 27        |

|          |      | 2.4.1     | Capacitors                         | 29        |

|          |      | 2.4.2     | Amplifier                          | 30        |

|          |      | 2.4.3     | Switch                             | 31        |

|          | 2.5  |           | urators                            | 32        |

|          | 2.6  | -         |                                    | 33        |

| 0        | D.   | 11.       |                                    | 0.5       |

| 3        |      | el desig  |                                    | <b>35</b> |

|          | 3.1  |           | ology characteristics              | 36        |

|          |      | 3.1.1     | Core transistors                   | 36        |

|          | 0.0  | 3.1.2     | IO transistors                     | 37        |

|          | 3.2  |           | eceptor circuit                    | 39        |

|          |      | 3.2.1     | Range of photocurrent              | 39        |

|          |      | 3.2.2     | Photoreceptor transistor           | 41        |

#### TABLE OF CONTENTS

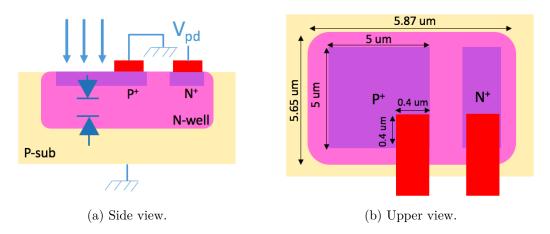

|    |        | 3.2.3    | Photodiode area                         | . 43 |

|----|--------|----------|-----------------------------------------|------|

|    |        | 3.2.4    | Dark current                            | . 43 |

|    |        | 3.2.5    | Bias point                              | . 47 |

|    |        | 3.2.6    | Process-Temperature corners simulations | . 49 |

|    |        | 3.2.7    | Monte-Carlo simulation                  | . 51 |

|    |        | 3.2.8    | Contrast sensitivity                    | . 53 |

|    |        | 3.2.9    | Design summary                          | . 53 |

|    | 3.3    | Buffer   |                                         | . 54 |

|    | 3.4    | Switche  | ed capacitor amplifier                  | . 56 |

|    |        | 3.4.1    | Sizing of capacitors                    | . 56 |

|    |        | 3.4.2    | Design of the amplifier                 | . 57 |

|    |        | 3.4.3    | Switch design                           | . 59 |

|    | 3.5    | Compa    | rators and Logic                        |      |

|    |        | 3.5.1    | Logic chain                             | . 62 |

| 4  | Valid  | dation a | and Characterization                    | 63   |

|    | 4.1    | Validat  | ion                                     | . 64 |

|    | 4.2    | Charac   | terization                              | . 67 |

|    |        | 4.2.1    | Dynamic range                           | . 67 |

|    |        | 4.2.2    | Minimum latency                         | . 67 |

|    |        | 4.2.3    | Fixed pattern noise                     |      |

|    |        | 4.2.4    | Power consumption                       | . 69 |

|    |        | 4.2.5    | Pixel Complexity                        | . 70 |

|    |        | 4.2.6    | Pixel area                              | . 70 |

|    |        | 4.2.7    | Fill factor                             | . 71 |

|    |        | 4.2.8    | Pixel scalability                       |      |

|    |        | 4.2.9    | Summary                                 | . 71 |

| 5  | Disc   | ussion   | and Perspectives                        | 73   |

|    | 5.1    |          | ion                                     | . 74 |

|    |        | 5.1.1    | Minimum Latency                         |      |

|    |        | 5.1.2    | Fill Factor                             |      |

|    |        | 5.1.3    | Thresholds                              |      |

|    | 5.2    | Perspec  | ctives                                  |      |

| Co | nclus  | sion     |                                         | 79   |

| Bi | bliogi | raphy    |                                         | 81   |

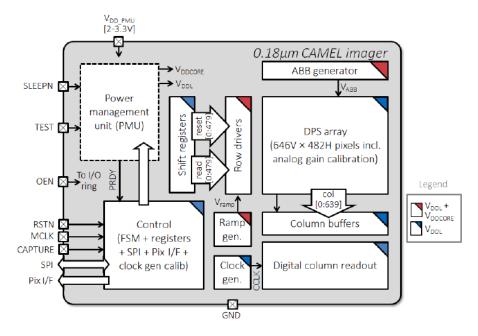

| Δr | nend   | lix A (  | CAMEL                                   | 85   |

| _  | _      |          |                                         |      |

| Aŗ | pend   | lix B S  | Single-stage CMOS operational amplifier | 87   |

| Aŗ | pend   | lix C I  | Photodiode layout                       | 91   |

| Aŗ | pend   | lix D I  | Eldo script                             | 93   |

## ACKNOWLEDGEMENT

Je voudrais remercier plusieurs personnes sans qui ce TFE ne serait pas aussi abouti aujourd'hui. Malgré que ce travail soit rédigé en anglais, je tenais à réaliser ces remerciements en français afin de pouvoir m'exprimer plus aisément.

Tout d'abord, je tiens à remercier mon promoteur, le Professeur David Bol ainsi que mon co-promoteur, le Professeur Denis Flandre pour leur soutien et leur disponibilité tout au long de ce mémoire. Nos réunions régulières m'ont permis de maintenir un bon rythme de travail durant toute l'année académique. Celles-ci m'ont également fourni un feedback régulier et des occasions pour poser mes questions. Ainsi, elles m'ont permis d'avancer continuellement dans mes recherches et de ne pas rester longtemps bloquée sur un même point. Un grand merci également à Charlotte d'avoir participé activement à chacune de ces réunions. Tes conseils, tant au sujet du domaine neuromorphic que sur la réalisation d'un mémoire en général, m'ont été d'une grande aide. Merci également pour ton soutien et ton intérêt continu à mon TFE. Finalement, merci de m'avoir convaincue et motivée de choisir cette proposition de mémoire l'année dernière. Cette initiation au neuromorphic a été pour moi une belle découverte. Je voudrais ensuite remercier Thomas pour sa grande disponibilité et son aide pour m'initier avec les outils mis à ma disposition. Merci également d'avoir partagé avec moi tes connaissances sur la technologie 0.18 μm CMOS. Ta présence m'a fait gagner un temps considérable lors de la réalisation de ce travail. Merci également au Professeur Jean-Didier Legat pour avoir accepté d'être le lecteur de mon TFE.

Enfin, je tiens à remercier mes proches d'avoir toujours été là pour moi tout au long de la réalisation de ce TFE. Merci à Elisabeth, Roselien et Fanny qui ont vécu cette période de mémoire avec moi. Notre soutien mutuel m'a permis de garder la motivation tout au long de cette période. Maman, Papa, Sophie, merci de m'avoir supportée dans mes moments de doute. Même si ce travail est surement toujours un peu flou pour vous, merci de vous y être intéressés et de m'avoir continuellement encouragée. Merci également d'avoir toujours cru en moi tout au long de mon parcours universitaire. Votre présence a été pour moi indispensable. Finalement, je voudrais te remercier Baptiste. En plus de tes précieux conseils, ta présence m'a permis de me détendre et de me rassurer dans mes moments difficiles. Merci d'être là pour moi quotidiennement ...

Naomi

## ABSTRACT

The recent interest in modelling the human retina opens the doors to neuromorphic imagers. Neuromorphic engineering succeeds in achieving a biomimetic retina by providing an electrical model as close as possible to neuron architectures involved in the vision process: the event-based dynamic vision sensor (DVS) is designed for low-data and low-power image sensing acquisition. Its particularity resides in asynchronous pixels responding only to relative changes in light intensity. These sensors show a wide dynamic range, low power consumption and good time resolution. The visual neuromorphic field is thus not only promising for robotics, but also for real-time tracking.

Dynamic vision sensors seem suitable for detecting sparse data acquisition but raise one question: how to efficiently decrease the power consumption of an asynchronous pixel responding only to relative changes in light intensity? Inspired from a state-of-the-art image sensor, this study proposes a new DVS design in a mature 0.18  $\mu$ m CMOS technology to tackle this challenge. Three different figures of merit are targeted: the dynamic range (to be maximized), the pixel area (to be minimized) and the power consumption (to be minimized). Moreover, compared to the state-of-the-art DVS working at 1.8 V or above, the main constraint added to this study is a supply voltage of 0.75 V to be compatible with the CAMEL image sensor from UCL. Pixel simulations show a detection in light changes of 10% with 3% of contrast matching. Moreover, the reported dynamic range is 140 dB. Finally, this new design provides a decrease of static power consumption from more than one order of magnitude (from 690 nW to 20.54 nW), at the expense of an increase in pixel latency of 42  $\mu$ s.

## LIST OF FIGURES

| 1.1  | Simplified schema of the human retina                                                                                        |

|------|------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Silicon energy bandgap                                                                                                       |

| 1.3  | P-N junction                                                                                                                 |

| 1.4  | General-purpose AER protocol for the transmission of data from an array of senders to an array of receivers                  |

| 1.5  | Control sequences of the AER data communication                                                                              |

| 1.6  | Mallik's pixel architecture.                                                                                                 |

| 1.7  | Pixel schematic and principles of operation of a 120 dB and 15 µs latency asynchronous temporal contrast vision sensor       |

| 1.8  | Schematic view of the ATIS architecture                                                                                      |

| 1.9  | DAVIS pixel schematic                                                                                                        |

| 2.1  | Schema of the pixel architecture studied in this Master Thesis                                                               |

| 2.2  | Pixel principles of operation                                                                                                |

| 2.3  | Cross section of the photodiode types                                                                                        |

| 2.4  | Schema of the different light scales                                                                                         |

| 2.5  | Conversion from surface to apparent surface                                                                                  |

| 2.6  | Schema of the switched capacitor amplifier                                                                                   |

| 2.7  | Switched capacitor amplifier circuit with switch closed and opened respectively                                              |

| 2.8  | Capacitor layout for matching issues                                                                                         |

| 2.9  | Single stage OTA architecture                                                                                                |

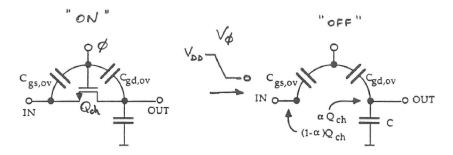

| 2.10 | Charges injection                                                                                                            |

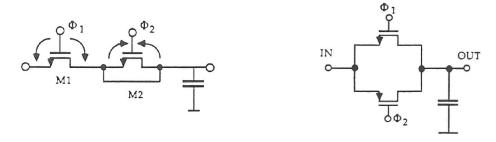

| 2.11 | Charges injection cancellation                                                                                               |

| 2.12 | Schema of the logic chain                                                                                                    |

| 2.13 | Principles of operation of the AER protocol used in the DAVIS                                                                |

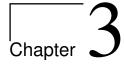

| 3.1  | gm/ID characteristic curve of NMOS core transistors                                                                          |

| 3.2  | Logarithm of NMOS core transistors drain current in various gate voltages                                                    |

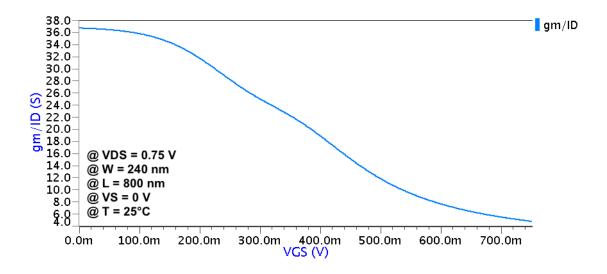

| 3.3  | gm/ID characteristic curve (top) and logarithm of the drain current (down) for a NMOS IO transistor in various gate voltages |

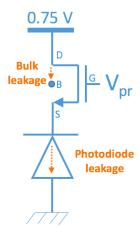

| 3.4  | Schema of the photoreceptor circuit responsible for the transduction from the photocurrent to the voltage $V_{pr}$           |

| 3.5  | Responsivity comparison of different photodiode types at different diffusion area                                            |

| 3.6  | Drain current variation in various gate voltages $V_{pr}$ for different photoreceptor core                                   |

|      | transistor widths and lengths.                                                                                               |

| 3.7  | Drain current variation in various gate voltages $V_{pr}$ for different photoreceptor IO                                     |

|      | transistor widths and lengths.                                                                                               |

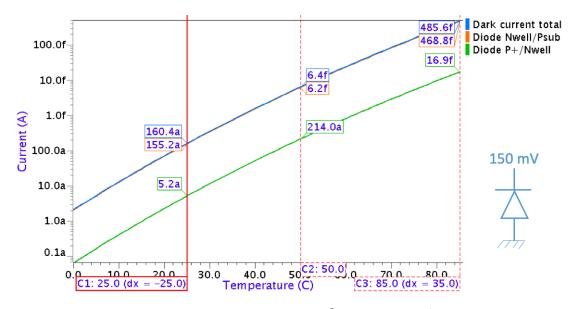

| 3.8  | Dark current of the photoreceptor circuit                                                                                    |

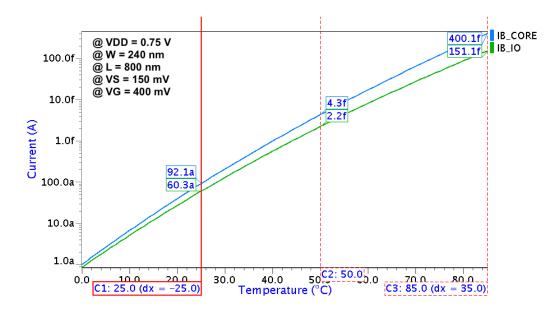

| 3.9  | Bulk current of an IO and a core photoreceptor transistor of 240 nm x 800 nm in                                              |

| 0    | various temperatures                                                                                                         |

| 3.10 | Side and upper views of the $p^+/n$ -well/ $p$ -sub type photodiode                                                          |

#### LIST OF FIGURES

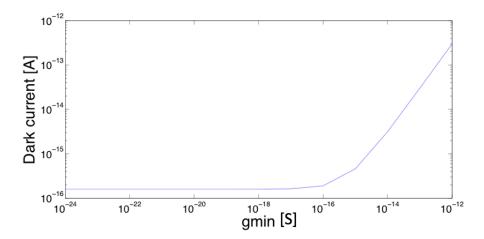

| 3.11        | Simulation of the photodiode leakage for a $p^+/n$ -well/ $p$ -sub type photodiode with diffusion area of 25 $\mu$ m <sup>2</sup> for different values of the gmin parameter | 46 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0.10        |                                                                                                                                                                              | 40 |

| 3.12        | Dark current simulation of a 25 $\mu$ m <sup>2</sup> diffusion area $p^+/n$ -well/ $p$ -sub type photodiode at different temperatures                                        | 46 |

| 3.13        | Dark current simulation of a 25 $\mu$ m <sup>2</sup> diffusion area $p^+/n$ -well/ $p$ -sub type photodi-                                                                    |    |

|             | ode at different bias voltages                                                                                                                                               | 47 |

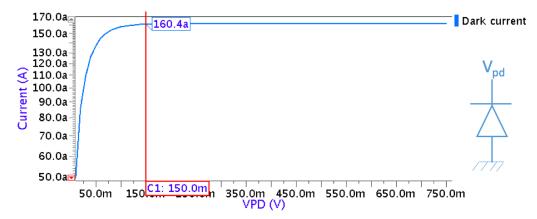

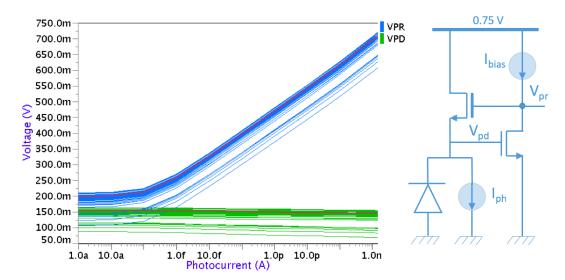

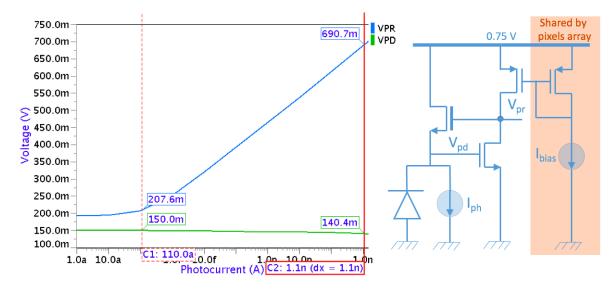

| 3.14        | $V_{pd}$ and $V_{pr}$ voltages versus the photocurrent in various bias transistor sizes                                                                                      | 47 |

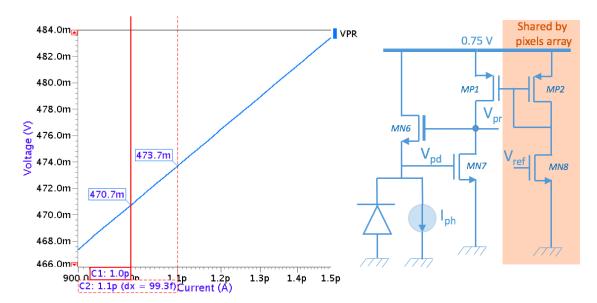

| 3.15        | Photoreceptor circuit characteristic curves                                                                                                                                  | 48 |

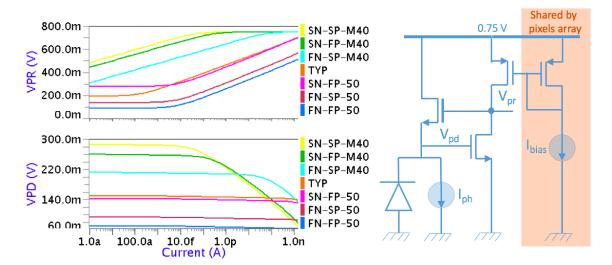

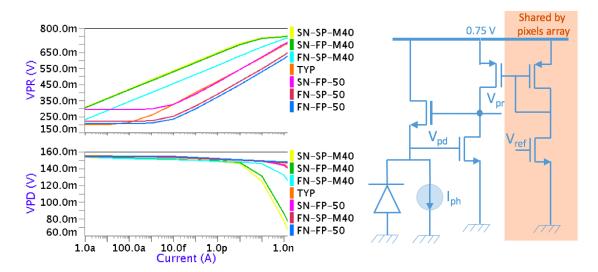

| 3.16        | Simulation of the variation in Process-Temperature corners of the photoreceptor                                                                                              |    |

| 3.17        | circuit                                                                                                                                                                      | 49 |

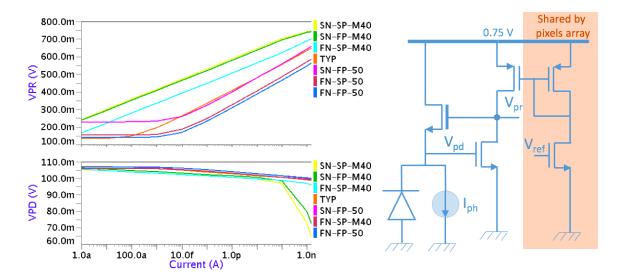

|             | circuit with a voltage reference source.                                                                                                                                     | 50 |

| 3.18        | Simulation of variation in Process-Temperature corners of the photoreceptor circuit with a voltage reference source at 100 mV                                                | 51 |

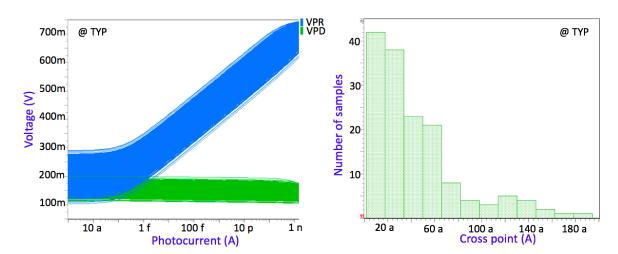

| 3.19        | Characteristic curves and histogram of the photoreceptor circuit simulated with a                                                                                            |    |

| 2.00        | Monte-Carlo simulation with 10,000 runs                                                                                                                                      | 51 |

| 3.20        | Characteristic curves and histogram of the photoreceptor circuit simulated with a Monte-Carlo simulation with 10,000 runs for a Slow NMOS - Slow PMOS process                |    |

|             | at -40°C                                                                                                                                                                     | 52 |

| 3.21        | Characteristic curve used to determine the sensitivity of the photoreceptor circuit.                                                                                         | 53 |

| 3.22        | Pixel schematic with the buffer highlighted                                                                                                                                  | 54 |

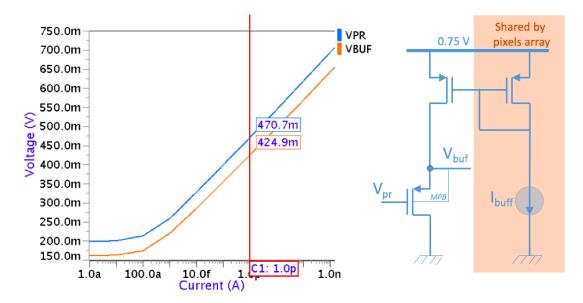

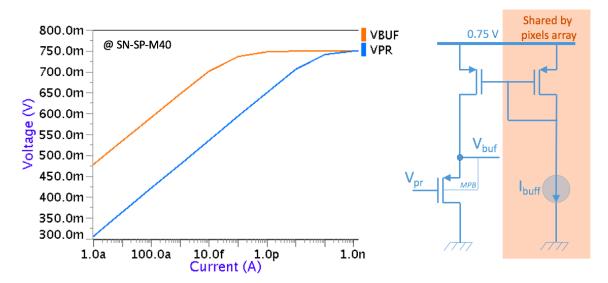

| 3.23        | Simulation of the buffer architecture                                                                                                                                        | 55 |

| 3.24        | Simulation of the buffer architecture in Slow NMOS - Slow PMOS corner at -40°C.                                                                                              | 55 |

| 3.25        | Pixel schematic with the switched capacitor amplifier circuit highlighted                                                                                                    | 56 |

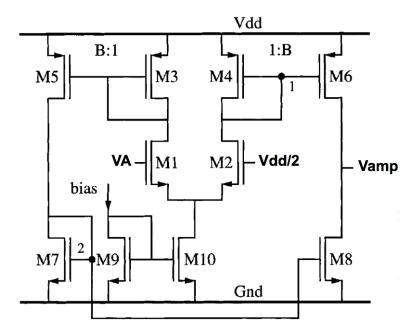

| 3.26        | CMOS operational amplifier used in SCA                                                                                                                                       | 57 |

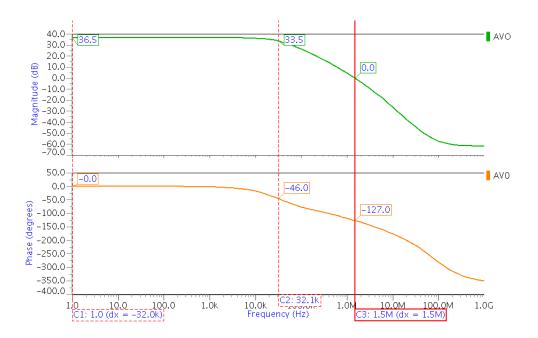

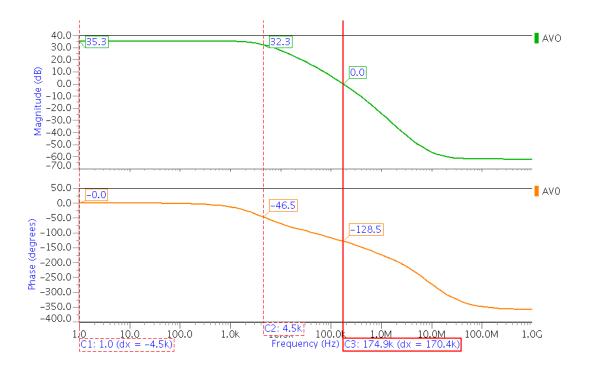

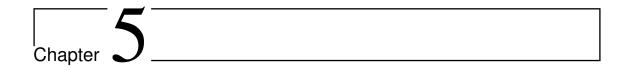

| 3.27        | Frequency response in open loop of the amplifier used in the switched capacitor amplifier circuit.                                                                           | 58 |

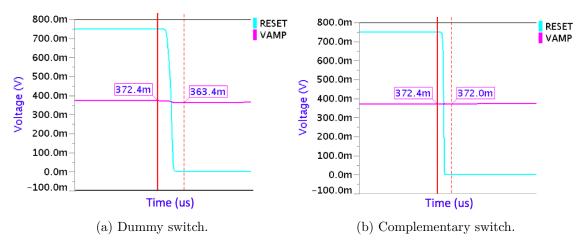

| 3.28        | Simulation of the charges injection during the reset of SCA with a dummy switch                                                                                              | 9C |

| 3.20        | at left and a complementary switch at right.                                                                                                                                 | 59 |

| 3.29        | Pixel schematic with the comparators highlighted                                                                                                                             |    |

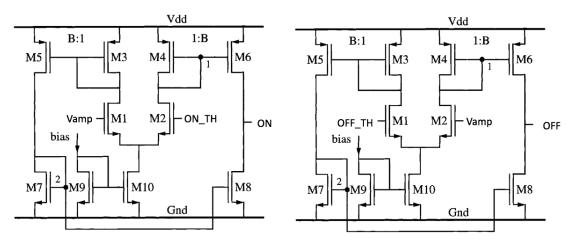

| 3.29 $3.30$ | Architecture of the two comparators                                                                                                                                          | 60 |

| 3.31        | Frequency response of the amplifier used in the two comparators with a load ca-                                                                                              | 61 |

| 0.00        | pacitor of 2 fF                                                                                                                                                              | 61 |

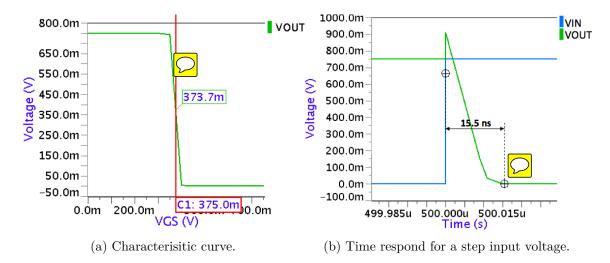

| 3.32        | Characteristic curve and time response of an inverter                                                                                                                        | 62 |

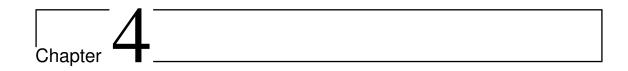

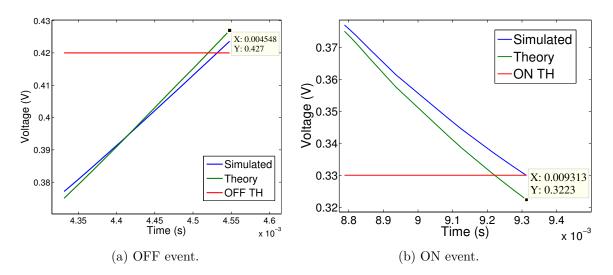

| 4.1         | Graph of the simulated and theoretical curves of Vamp between two reset signals.                                                                                             | 64 |

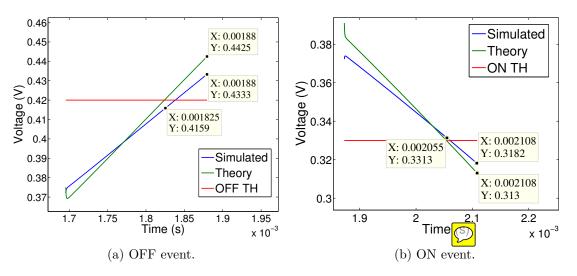

| 4.2         | Simulation of the change in $V_{pr}$ between two events                                                                                                                      | 66 |

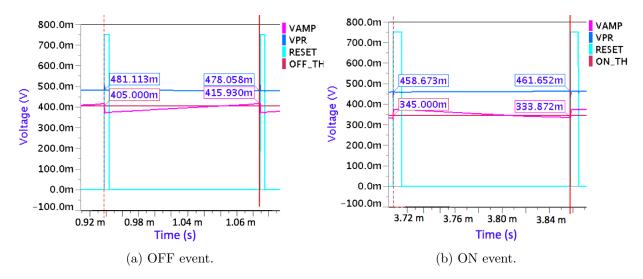

| 4.3         | Response time of the pixel excited with a current step at 1 klx                                                                                                              | 67 |

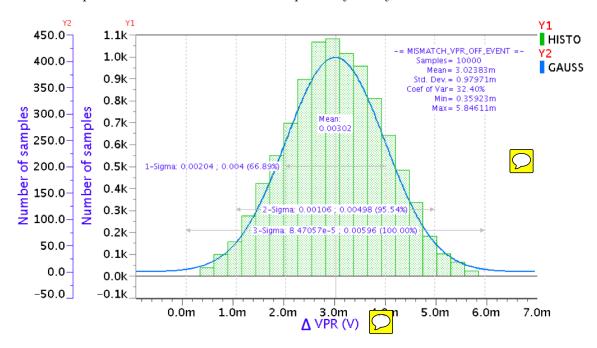

| 4.4         | Histogram of the change in $V_{pr}$ between two OFF events                                                                                                                   | 68 |

| 4.5         | Histogram of the change in $V_{pr}$ between two ON events                                                                                                                    | 68 |

| 5.1         | Frequency response in open loop of the modified amplifier                                                                                                                    | 76 |

| 5.2         | Graph of the simulated and theoretical curves of Vamp between two reset signals                                                                                              |    |

|             | with modified amplifiers                                                                                                                                                     | 76 |

| A.1         | Architecture of the ultra-low power VGA time based CMOS imager codename                                                                                                      | 0. |

|             | "CAMEL"                                                                                                                                                                      | 85 |

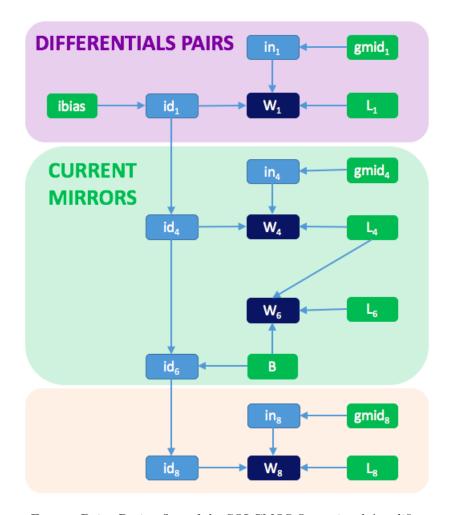

| B.1         | Design flow of the SOI CMOS Operational Amplifier                                                                                                                            | 87 |

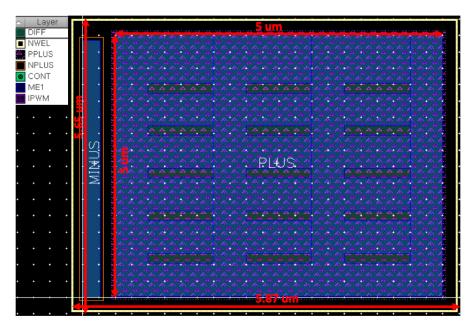

| C.1         | DIOP_MM layout                                                                                                                                                               | 91 |

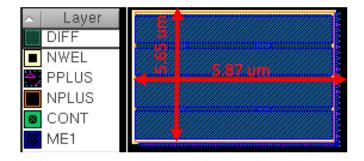

| C.2         | DIONW_MM layout                                                                                                                                                              | 91 |

## LIST OF TABLES

| 1.1        | Summary of state-of-the-art architectures                                                                                                               | 18 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1        | Norm of some illuminance intensities                                                                                                                    | 25 |

| 3.1<br>3.2 | Characteristic of core an IO transistors in a $0.18~\mu\text{m}^2$ technology Norm of some illuminance intensities and their corresponding photocurrent | 38 |

| J          | per unit of area.                                                                                                                                       | 40 |

| 3.3        | Norm of some illuminance intensities and their corresponding photocurrent                                                                               |    |

|            | for a photodiode area of 25 $\mu m^2$                                                                                                                   | 43 |

| 3.4        | Summary of transistor size in the photoreceptor circuit                                                                                                 | 53 |

| 3.5        | Summary of transistor size used in the amplifier of the SCA circuit                                                                                     | 59 |

| 4.1        | Change in $V_{pr}$ between two events                                                                                                                   | 66 |

| 4.2        | Comparison between our pixel and the state-of-the-art architectures                                                                                     |    |

| 5.1        | Example of transistors size used to increase the DC gain of the amplifiers                                                                              | 75 |

| A.1        | Performance result comparison between CAMEL and SunPixer                                                                                                | 86 |

## LIST OF ACRONYMS

**AER** Address-Event Representation

**APS** Active Pixel Sensor

ATIS Asynchronous Time-based Image Sensor

BSI Backside illumination

CIS CMOS Image Sensor

CCD Charge-Coupled Device

CMOS Complementary Metal Oxide Semiconductor

DAVIS Dynamic and Active pixel Vision Sensor

**DPS** Dynamic Pixel Sensor

**DR** Dynamic Range

DVS Dynamic Vision SensorEHP Electron-Hole PairFPN Fixed-Pattern-Noise

MC Monte-Carlo

MIMCAP Metal-Insulator-Metal Capacitor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NMOS n-channel MOSFET

OTA Operational Transconductance Amplifier

PMOS p-channel MOSFETPWM Pulse-Width-Modulation

SCA Switched Capacitors Amplifier

SR Slew rate

VGA Video Graphics Array

### Introduction

Since the early stages of evolution, we use our eyes to see our environment. They are even more important to prevent us from danger. For example, when a ball is thrown in our face, the brain can manage to avoid the collision thanks to the information received from our eyes. The visual system is therefore fundamental for survival.

Many researches have already investigated a way to model the human retina. Indeed, frame-based image sensors, that capture static light intensity, are widely deployed [1, 2]. However, they suffer from a high power consumption due to continuous data acquisition. Thus, a new sensor type has emerged: the neuromorphic image retina. It aims to give an electrical model as close as possible to neuron architectures involved in the biological vision process.

The first bio-inspired image sensor was designed in 1993 by M. Mahowald [3]. Even though its study was not adapted for any real task, it was an inspiration for many future neuromorphic works [4, 5, 6]. Hence, the event-driven dynamic vision sensor (DVS) was proposed [7]. The idea behind this new kind of sensor is to reduce redundant data by creating asynchronous pixels responding only to relative changes in light intensity. In this way, when a sparse data acquisition is detected, only the relevant data is processed. Keeping our example of the ball thrown in our face, this means that we only care now about the ball itself and not about the surrounding static environment. Works on DVS have already reported a wide dynamic range (120 dB), low power consumption (0.12  $\mu$ W/pixel at low activity), low latency (only 3  $\mu$ s) and a good temporal precision [5, 6]. The DVS features then get closer to the ones of human eyes. An event-driven dynamic vision sensor has already been implemented in a robot playing ping-pong [8] as well as in a pencil balancing robot [9]. The visual neuromorphic field is thus not only promising for robotics, but also for real-time tracking [10].

Therefore, this work aims to answer the following questions.

- How can the human eye be electrically emulated for event-driven sparse data acquisition?

- How to efficiently decrease the power consumption of an asynchronous pixel responding only to relative changes in light intensity?

#### Targets, contributions and outline

The purpose of this study is to understand the different DVS architectures proposed in the literature and to identify their strengths and weaknesses. Based on this, an asynchronous pixel architecture that responds only to relative changes in light intensity is proposed and implemented in a  $0.18 \mu m$  CMOS technology, targeting the following three figures of merit:

- dynamic range (to be maximized),

- pixel area (to be minimized),

- power consumption (to be minimized).

Moreover, compared to state-of-the-art DVS architectures working at 1.8 V or above, the main constraint added to this study is a supply voltage of 0.75 V to be compatible with the CAMEL image sensor from UCL [1]. The main contributions from this work are:

- a complete state of the art of the different DVS architectures,

- a methodology providing guidelines to follow during the design of an asynchronous pixel for sparse vision data acquisition,

- a neuromorphic pixel designed in a  $0.18~\mu m$  CMOS technology under 0.75~V supply voltage and its comparison with the literature that reveals a wider dynamic range and a lower power consumption.

These contributions are organized into five chapters:

- Chapter 1: The fundamentals as well as the state of the art are presented. The different concepts used during this Master Thesis are briefly reviewed. Then, contributions from prior researches are introduced and their main advantages and drawbacks are highlighted.

- Chapter 2: A neuromorphic pixel architecture is studied and essential guidelines to follow for its design are provided. Moreover, the equations behind its different circuit blocks are established.

- Chapter 3: The pixel is designed in a mature 0.18 μm CMOS technology with a supply voltage of 0.75 V. Simulations of each circuit block are given.

- Chapter 4: The pixel designed in Chapter 3 is fully validated and characterized in order to compare its performances with the state-of-the-art architectures.

- Chapter 5: Different trade-offs are discussed before giving some perspectives for future works.

|              | 1 | - |  |  |  |

|--------------|---|---|--|--|--|

| l<br>Chapter |   |   |  |  |  |

## Fundamentals and state of the art

#### Contents

| 1.1 | Human Retina                             |

|-----|------------------------------------------|

|     | 1.1.1 Architecture                       |

|     | 1.1.2 Characteristics                    |

| 1.2 | Photodiode                               |

|     | 1.2.1 Principles of operation            |

|     | 1.2.2 Figures of merit                   |

| 1.3 | Address-Event Representation             |

| 1.4 | Previous neuromorphic CMOS image sensors |

|     | 1.4.1 Synchronous architectures          |

|     | 1.4.2 Asynchronous architectures         |

|     | 1.4.3 Summary                            |

|     |                                          |

This first chapter aims to recall/explain some essential concepts required for a better understanding of this Master Thesis. Moreover, it gives an overview of the different architectures implementing a neuromorphic CMOS imager for sparse vision data acquisition. Firstly, the human retina architecture is presented in order to understand the challenges of a neuromorphic image sensor. Then, the photodiode principles of operation are analyzed and its important features are listed. Afterwards, the address-event representation (AER) used as an asynchronous communication protocol between neuromorphic chips is described. Finally, different state-of-the-art pixel architectures implemented for sparse vision data acquisition are presented from the oldest to the most recent one.

#### 1.1 Human Retina

To develop a neuromorphic vision sensor, it is first essential to review the architecture and characteristics of the human retina. In this way, the different challenges to overcome are pointed out.

#### 1.1.1 Architecture

The human retina is a thin sheet of neural tissue which recovers the orb of the eye. It is responsible for collecting the visual information and to send it to the brain in the form of spikes. A schema of the retina is presented in Figure 1.1.

FIGURE 1.1 – Simplified schema of the human retina (from [11]).

In Figure 1.1, light comes from the left and goes to the back of the eye. It is sensed and transduced into an electrical signal by the photoreceptor cells (the cones for day vision and the rods for night vision) while the horizontal cells capture the background illuminance. Afterwards, the bipolar cells amplify the difference between the photoreceptor and the horizontal cells outputs. The signal is finally transferred to the ganglion cells that transform the electrical signal into an action potential before to send it to the brain [3].

#### 1.1.2 Characteristics

As human eyes can be exposed to different illumination levels, the retina must send reliable information over a wide range of light intensities. Experiments on mudpuppy retinae confirmed this wide input range property of photoreceptors cells [12]. Theses experiments have also discovered that the transduction from the sensed light into a voltage is performed by a logarithmic relationship. Finally, according to a video realized by S. Liu, the human eye is composed of 10<sup>8</sup> photoreceptors and 10<sup>6</sup> ganglion cells spiking outputs. Moreover, it has a dynamic range of 180 dB and consumes only 3 mW [13]. Hence, reaching these same performances is a huge challenge for an artificial retina.

#### 1.2 Photodiode

The creation of an artificial retina required a photodetector element to sense the surrounding light intensity. The principles of operation of this element as well as some of its figures of merit are presented in this division.

#### 1.2.1 Principles of operation

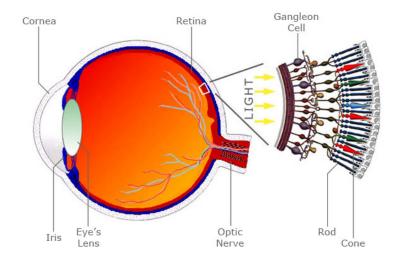

An artificial retina is an image sensor composed of a two-dimensional array of pixels. Each of the pixel converts the incident light at its surface to an electrical signal thanks to a photodetector element. The photodetector is then a semiconductor that captures light particles (photons). The main principle of this element rests on the photoelectric effect. When the photodetector is lighted, the photons are either reflected or absorbed by the semiconductors. The absorbed light particles excite the electrons and if the energy is higher than the energy gap  $E_g$ , the electrons move from the valence band  $E_v$  into the conduction band  $E_c$  creating an electron-hole pairs (EHP) [14]. This phenomenon is represented in Figure 1.2.

FIGURE 1.2 – Silicon energy bandgap (from [14]).

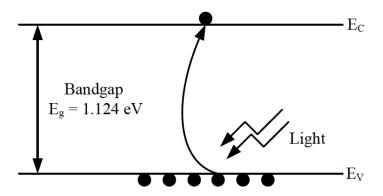

A well-known photodetector, that is used in this study to capture light information, is the photodiode. A photodiode is composed of a reverse biased p-n junction that generates a photocurrent. The p-n junction is obtained when a n-type semiconductor (characterized by an excess of electrons) and a p-type semiconductor (characterized by an excess of holes) are placed in contact. The electrons/holes diffuse from the n-type/p-type semiconductor to the p-type/n-type semiconductor due to the concentration gradient. The diffusion stops when the electric field of the carriers is equal to the concentration gradient, which is called the equilibrium. When this equilibrium is reached, the junction is formed. If the junction is reverse biased, this creates a depletion region between p-type region and n-type region [14, 15, 16]. A schema of the reverse biased pn-junction and its current-voltage characteristic curve are given respectively in FIGURE 1.3a and 1.3b.

- (a) P-N junction in reverse biased (from [17]).

- (b) I-V characteristic of a p-n junction (from [18]).

Figure 1.3 - P-N junction.

Due to the electric field existing across the depletion region, when the photodiode is lighted, the photons absorbed in the depletion region create electron-hole pairs (EHP) that generate the photocurrent. Before giving the equation of the photocurrent, some parameters are defined [14, 15, 16, 19]:

- q is the electric charge  $(q \simeq 1.6 \times 10^{-19} C)$ ,

- k is the Boltzmann constant  $(k \simeq 1.38 \times 10^{-23} JK^{-1})$ ,

- T is the absolute temperature,

- A is the total junction area,

- $\epsilon_s$  is the silicon permittivity ( $\epsilon_s = 11.9$ ),

- $N_{A,D}$  is the doping concentration of p-type and n-type semiconductors respectively,

- $g_{op}$  is the light induced rate of EHP generation,

- $n_i$  is the intrinsic carrier concentration of silicon ( $n_i = 1.38 \times 10^10 cm^{-3}$  at 300K),

- $m_{n,p}$ \* is the effective mass of the electron and hole respectively,

- $\tau_{n,p}$  represents the recombination lifetime for electrons and holes respectively,

- $\mu_{n,p}$  is the electron mobility in the conduction band and hole mobility in the valence band respectively. It can be expressed by EQUATION 1.1,

$$\mu_{n,p} = \frac{q\tau_{n,p}}{m_{n,p}*} \tag{1.1}$$

-  $D_{n,p}$ , expressed by EQUATION 1.2, is the diffusion coefficient of electrons and holes respectively,

$$D_{n,p} = \mu_{n,p} \frac{kT}{q} \tag{1.2}$$

-  $L_{n,p}$  is the electron and hole diffusion length respectively. It can be expressed by the Equation 1.3,

$$L_{n,p} = \sqrt{2D_{n,p}\tau_{n,p}} \tag{1.3}$$

-  $\phi_0$  is the internal potential expressed by Equation 1.4,

$$\phi_0 = \frac{kT}{q} ln(\frac{N_A N_D}{n_i^2}) \tag{1.4}$$

- W is the depletion region width. It depends on the doping concentration of p-type  $(N_A)$  and n-type  $(N_D)$  semiconductors used to create the p-n junction and on the voltage V applied across it. Its equation is given in EQUATION 1.5.

$$W = \sqrt{\frac{2\epsilon_s}{q}(\phi_0 - V)\frac{N_A + N_D}{N_A N_D}}$$

(1.5)

Hence, the current due to optically generated carriers  $I_{op}$  can be written as EQUATION 1.6.

$$I_{op} = q \ g_{op} \ A \ (W + L_n + L_p)$$

(1.6)

The generation of EHP depends on the light wavelength and on the penetration depth of the light particle into the material. The light intensity of a photon at depth x can be expressed as EQUATION 1.7.

$$I(x) = I_0 \exp(\alpha x) \tag{1.7}$$

with  $I_0$  the light intensity at the surface of the semiconductor and  $\alpha$  the coefficient of absorption.

#### 1.2.2 Figures of merit

During this study, different figures of merit related to photodiodes are used to characterize neuromorphic pixels. The definition of each of them is reminded hereunder [19, 20].

**Fill Factor** The fill factor is the percentage of the area occupied by the photodiode in the pixel.

**Responsivity** In this study, the responsivity expressed the ratio of the photocurrent to the optical input power  $[A/Wcm^{-2}]$ .

**Dark current** The dark current is the current generated under dark conditions. It can also be defined as the leakage current of the photodiode and connected devices. The dark current is due to several sources as thermal generation in the depletion region, thermal generation due to defects on the surface of the diode, etc. If  $g_{th}$  is the thermal rate of EHP generation, photodiode leakage current can be expressed as EQUATION 1.8:

$$I_{dark} = q g_{th} A (W + L_n + L_p)$$

$$\tag{1.8}$$

**Dynamic range** The dynamic range (DR) is defined as the ratio between the largest and lowest photocurrent detectable by the sensor.

Efficiency The external quantum efficiency defines the conversion from incident photons to electrons. It can be expressed as the product of optical efficiency and internal quantum efficiency. The first one represents the portion of absorbed photons in the semiconductor from the number of incident photons. The second one is the ratio between the number of induced charges and the number of incident photons. The photodiode efficiency depends also on the junction depth in the semiconductor. Actually, the EHP generated above the junction are much more likely to get collected that the ones generated under it as they start to spread deeper into the material, away from the junction. Hence, only a depth junction can generate EHP for long wavelength photons that penetrate deeper into the material. On the contrary, a junction relatively close to the surface captures only small wavelength photons. Finally, the collection efficiency depends also of the depletion region width as a wider one is more favorable to EHP generation.

**Junction capacitance** The junction capacitance  $C_j$ , that determines charge-to-voltage conversion, is defined by Equation 1.9.

$$C_j = \epsilon_s A/W \tag{1.9}$$

Hence, if the junction capacitance increases, the charge-to-voltage conversion decreases and inversely.

#### 1.3 Address-Event Representation

The Address-Event Representation (AER) is an asynchronous chip-to-chip and/or intrachip communication protocol that proposes a way to transmit spikes based signals between neuromorphic systems. Although the AER communication protocol is not developed in this Master Thesis, it is interesting to understand its principles of operation. Actually, in a future work, it could be implemented to this study. Hence, motivations to use such a protocol are pointed out in this section. Moreover, a brief explanation of its control sequences is given.

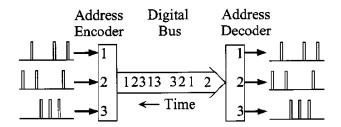

The AER protocol was first proposed in 1991 in a Ph.D Thesis of California Institute of Technology [21]. Since then it was used in many neuromorphic chips [5, 6]. This chip-to-chip communication protocol is inspired by biology. More specifically, it is inspired from neural networks in human brain where axons are replaced by digital circuits. The AER model for a unidirectional communication is schematized in FIGURE 1.4. Each neuron is represented by a unique binary address. Whenever a neuron of the transmitter chip spikes, the digital bus transmits its address to the receiver chip. Multiple neurons share then the same high-speed bus. When the receiver receives an address, it interprets it as an action potential that occurs on the corresponding neuron. Image sensors using the AER generate then an output in the form of address-events [3, 22].

FIGURE 1.4 – General-purpose AER protocol for the transmission of data from an array of senders to an array of receivers (from [22]).

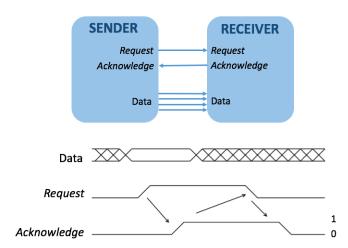

The control sequence of the data communication from a sender to a receiver is shown in Figure 1.5 and described hereunder. The request binary signal can only be driven by the sender and is exclusively sensed by the receiver and inversely for the acknowledge binary signal. The number of wires as well as the number of states of each wire are application dependent [23].

FIGURE 1.5 – Control sequence of the AER data communication (from [23]).

- In the inactive state, the sender drives the request signal to logic 0, the receiver drives the acknowledge signal to logic 0 and the data wires indicate data invalidity.

- When the sender wants to send a data to the receiver, it first drives a valid data on the data wires and then rises the request logic signal to 1. The receiver responds by sensing the valid data, which can take a relatively long time, and then rises the acknowledge logic signal to 1. This removes the requirement of the sender to put a valid data on the data wires.

- When the sender sensed an acknowledge signal to 1, it drives the request signal to logic 0 in a certain amount of time.

- When the receiver sensed that the request signal is at logic 0, it drives the acknowledge signal to logic 0 in a certain amount of time.

- Once the sender sensed that the acknowledge signal is at logic 0, it is free to start a new data communication.

#### 1.4 Previous neuromorphic CMOS image sensors

The story begins in 1993 when M. Mahowald, during its doctoral dissertation and under the guidance of C. Mead, constructed an analog system of the biological structures involved in vision. In 1994, he built the first AER vision sensor in a modified version of its Ph. D., spending from neurons to microcircuits [3]. Actually, during its researches, he had discovered that neural circuit can be better modeled by electronic circuits in CMOS technology than by conventional sequential computer languages. Thanks to the similarities between the biological system and Mahowald's analog system, comparisons between them become feasible. The analog circuit he proposed is composed of a phototransducting element, a resistive system and a differential amplifier. The function of these three elements is summarized hereunder.

- The phototransducting element generates a logarithmic relation between the sensed light intensity and the output current.

- The resistive system models the retina horizontal cells by spatially and temporally averaging the output of the phototransducting element.

- The differential amplifier models the retina bipolar cells outputs by making the difference between the phototransductor outputs and the horizontal cells signals.

Unfortunately, the system realized by M. Mahowald was not adapted for any real task as the CMOS technology was not mature enough to reach the quality of charge-coupled device (CCD) imagers. Moreover, its pixel area was too large to provide high-resolution while meeting a reasonable cost. However, it was the first multichip analog neuromorphic system that interacts directly with the environment. Hence, it had opened the door to the neuromorphic CMOS imager field.

In 2004, Zaghoul and Boahen proposed a pixel design which captures the key features of biological retinas [4, 24]. They have drawn inspiration from neural circuits to build their model, especially from the four main ganglion cell types found in the retina. Their chip realizes luminance adaptation, bandpass spatio-temporal filtering, temporal adaptation and contrast gain control. Moreover, as their goals were more to provide a model and a design based on the retina key features than create a practical device, the performances as energy efficiency and deviation from pixel-to-pixel were not optimized.

Two more practical vision sensor architectures came out in 2002 and 2005: the asynchronous architecture developed by Kramer [25] and the synchronous architecture proposed by Mallik *et al.* [26] respectively. Since the Krame's work has been modified by different studies to reach better performances [5, 6, 27]. The two kinds of architectures are described in more details hereunder, starting with the Mallik *et al.* synchronous architecture.

#### 1.4.1 Synchronous architectures

Mallik et al. developed a synchronous temporal change threshold detection imager in 2005 [26]. To achieve this purpose, they modified the traditional CMOS active pixel sensor (APS) to detect a change in illumination. The pixel architecture is represented in Figure 1.6.

FIGURE 1.6 – The Mallik's pixel architecture (from [28]).

Hence, the pixel developed, and modified in 2007 [28], integrates a three-transistors APS with a two-capacitors and three-transistors comparator in a mature  $0.5 \,\mu m$  CMOS technology. The comparator can be use either to detect scene changes or to perform, without any modifications, a pixel level analog-to-digital conversion. When using as a scene change detector, the comparator raises a digital flag each time the change between two frames of the analog APS output voltage reaches a variable threshold. As intensity change is detected by comparison of the current frame against the previous one, the event generation with this kind of architecture is synchronous. Moreover, although it uses a basic APS, the resulting dynamic range is poor and it results in absolute, rather than relative, illumination-change threshold. This architecture is therefore not really adapted for this Master Thesis as the asynchronous retina behavior is not emulated by the ATIS.

#### 1.4.2 Asynchronous architectures

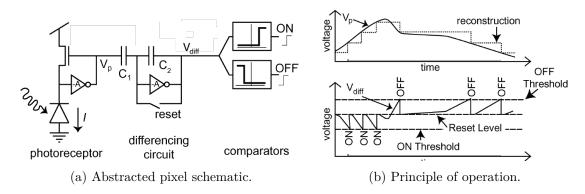

In 2002, Kramer developed a vision sensor in a 0.35 μm CMOS technology [25]. This sensor adapts itself to background illuminance and responds to local positive (ON) and negative (OFF) contrast changes. Two years later, P. Lichtsteiner *et al.* proposed an improved version of this imager by using a brighter pixel circuit and layout principles [29]. This modified sensor shows a wider dynamic range and responds much more symmetrical to ON and OFF events. However, the device presents a mismatch in transistors making it difficult to use at low contrast threshold. In 2008, a 120 dB and 15 μs latency asynchronous temporal contrast vision sensor was introduced by the same research group to overcome the previous issues [7]. The pixel is designed to achieve low mismatch, wide dynamic range, and low latency in a reasonable pixel area. The abstracted pixel and its principles of operation are illustrated in Figure 1.7a and Figure 1.7b respectively.

FIGURE 1.7 – Pixel schematic and principles of operation of a 120 dB and 15 μs latency asynchronous temporal contrast vision sensor [7].

To preserve the three key properties of biological vision, this architecture combines a photoreceptor with a differential circuit and two comparators. The logarithmic photoreceptor circuit modeled the retina rods and cones by producing an electric signal  $V_p$  from the sensed light. The bipolar cells are replaced with a differential circuit amplifying  $V_p$  change between two reset signals, with the amplification gain determined by the capacitor ratio  $C_1/C_2$ . Finally, the ganglion cells are modeled with two comparators. Each time the output voltage of the differential circuit  $(V_{diff})$  reaches one of the two comparators thresholds, the pixel creates an event leading to a reset of the differential circuit. Each pixel, independently from each other, produces therefore local sparse events in a continuous time. To be compatible with the AER protocol, these events appear at the pixel output as asynchronous digital addresses.

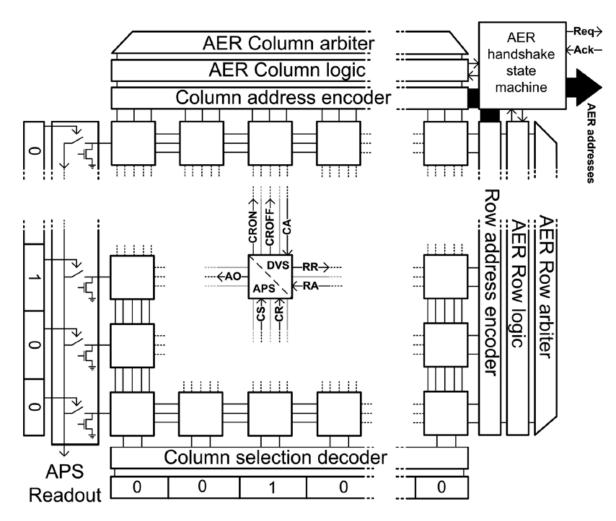

From this work, the dynamic vision sensor (DVS) is born. Since different vision sensors have been developed. In 2011, C. Posh *et al.* proposed an asynchronous time-based image sensor (ATIS) [6]. Barranco *et al.* came out with two asynchronous frame-free dynamic vision sensors in 2011 [30] and 2013 [27]. A dynamic and active pixel vision sensor (DAVIS) [5] and its color version (cDAVIS) [31] were introduced respectively in 2014 and 2016 by the Institute of Neuroinformatics at the University of Zurich and ETH Zurich. Finally, the Samsung group has recently proposed a VGA dynamic vision sensor. The different architectures are presented hereunder in chronological order.

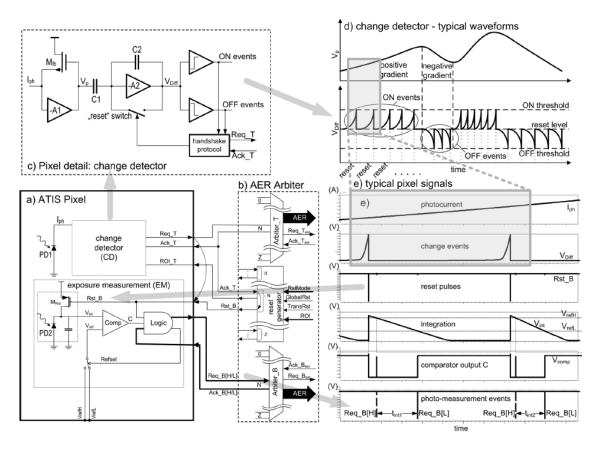

#### The asynchronous time-based image sensor

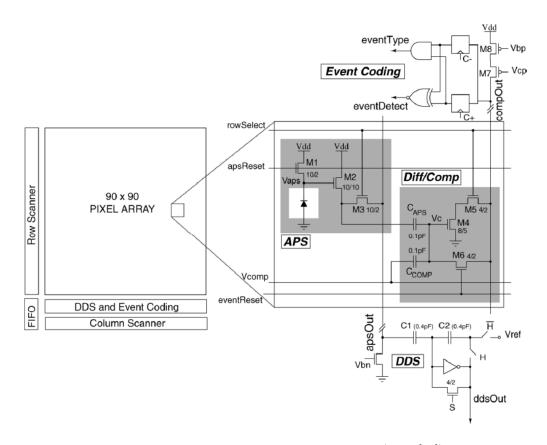

The asynchronous time-based image sensor (ATIS) schematized in FIGURE 1.8 is the first visual sensor to combine the "where" and "what" systems [6]. The imager integrates an array of pixels, each of them containing an event-based change detector and a pulse-width-modulation (PWM) exposure measurement circuit. The event-based change detection system is based on the dynamic vision sensor developed previously and allows to model the biological "where" system when an object motion is detected. The PWM exposure measurement system is used to provide details of visual information, modeling then the "what" system.

FIGURE 1.8 – Schematic view of the ATIS architecture (from [6]).

The exposure measurement system of the ATIS pixel is initialized only when the change detector of the same pixel detects a change in light intensity and produces the corresponding event. Therefore, the sensor does not generate redundant data when no events are detected. The visual information (temporal contrast and grayscale data encoded in interevent intervals) is communicated to the output channel in the form of an asynchronous AER protocol.

Benefits from this kind of architecture is a reduction in bandwidth, memory and power requirements for data transmission. However, its drawback is that each pixel used two photodiodes, one in the change exposure measurement system and one in the change detector.

#### A 3.6 ms latency asynchronous frame-free event-driven DVS

In 2011, Barranco et al. proposed a modified version of the dynamic vision sensor by adding a compact preamplification stage allowing to improve the minimum detectable contrast over previous design [30]. Each pixel still detects temporal contrast but a minimum change in light intensity of 10% can now be detected while at the same time reducing the pixel area by 1/3. Moreover, by using an alternative photo-sensing stage, the sensor latency is reduced to 3.6  $\mu$ s. However, the price to pay for these improvements is a significant increase in the power consumption and a slight increase in the fixed pattern noise (FPN). In 2013, they succeed in improving the contrast sensitivity down to 1.5% with a power consumption of 4 mW [27]. Moreover, the FPN is reduced to 0.9% and the overall area is further decreased while maintaining a good dynamic range (DR) and a latency of 3  $\mu$ s. Decreasing the contrast sensitivity improves the quality of the sensed scene as the sensor captures finer details as contours and textures. Although the price to pay for this improvement is the increase of the output events, it opens the doors to new applications such as high speed texture based recognition.

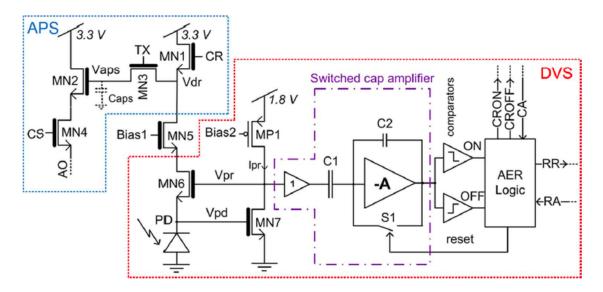

#### The dynamic and active pixel vision sensor

The asynchronous time-based image sensor (ATIS) contains motion artifacts at high-speed due to the use of its two photodiodes. To overcome this issue, a dynamic and active pixel vision sensor (DAVIS) was proposed by Brandli *et al.* in 2014 [5]. The pixel architecture developed in the DAVIS is represented in Figure 1.9. It integrates both a basic active pixel sensor (APS) and a modified version of the DVS developed by Lichtsteiner [7]. More interesting, the APS and the DVS share the same photodiode. Therefore, the DAVIS can produce concurrently asynchronous events (with the DVS part of the pixel) and synchronous absolute light information (with the APS part of the pixel).

FIGURE 1.9 – DAVIS pixel schematic (from [5]).

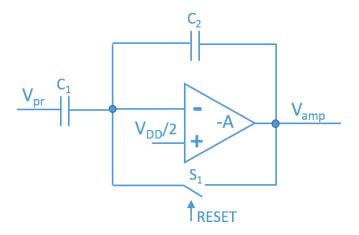

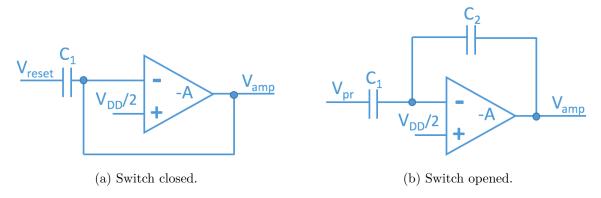

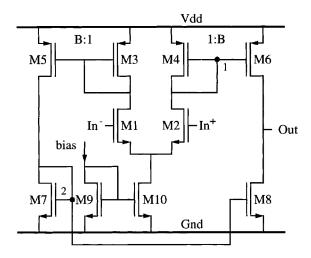

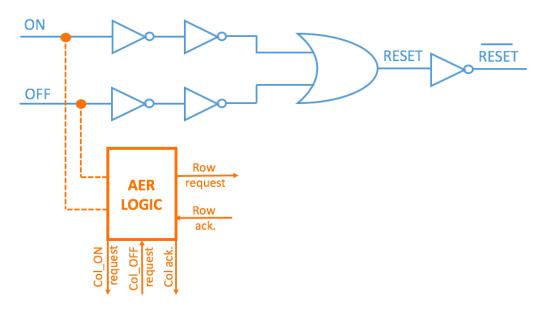

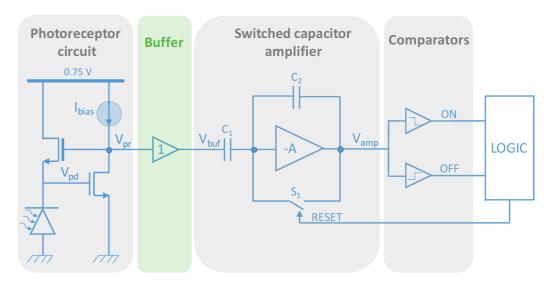

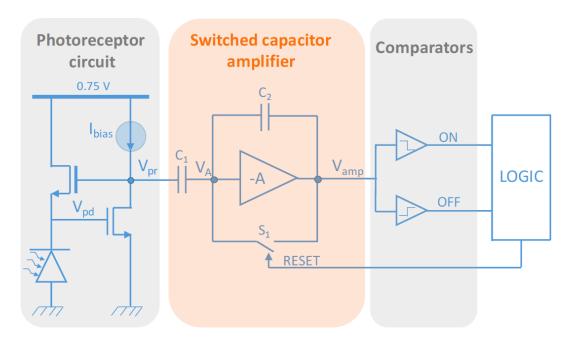

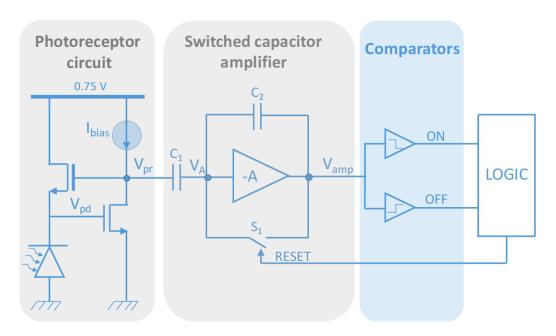

The DVS part of the pixel is composed of, from left to right, a photoreceptor circuit, a buffer, a switched capacitor amplifier circuit, two comparators and an AER logic. The different elements are explained hereunder.

- The photoreceptor circuit performs the logarithmic conversion between the photocurrent and its output voltage  $V_{pr}$ .

- The buffer allows to isolate the photoreceptor circuit from the reset of the switched capacitor amplifier.

- The switched capacitor amplifier (SCA) circuit amplifies the change in  $V_{pr}$  between two reset signals.

- The two comparators compare the amplified change in  $V_{pr}$  with an upper and a lower threshold. If the change reaches one of the two thresholds, an OFF or ON event is respectively produced.

- The AER logic resets the pixel when an event is produced and ask the access to the bus to send it to the rest of the chip.

This vision sensor is developed in a  $0.18 \,\mu m$  CMOS technology and reaches a contrast sensitivity of 11%, a dynamic range of  $130 \,dB$  and a minimum pixel latency of  $3 \,\mu s$ .

#### The colored dynamic and active pixel vision sensor

In 2016, a colored version of the DAVIS (cDAVIS) was proposed [31]. Each pixel of the cDAVIS combines monochrome event-generating DVS pixels and 3 APS pixels patterned with an RGBW color filter array. Therefore, the colored vision sensor is able to concurrently produce synchronous VGA resolution RGBW-coded frames and asynchronous monochrome QVA resolution temporal contrast events. Hence, with a slightly modified DAVIS pixel, the cDAVIS is able to capture the detail color while still tracking movements.

#### The Samsung's pixel

Recently, Samsung developed a VGA dynamic vision sensor [32]. The Samsung's pixel tries to reach thinner pixels as the DAVIS pixel size of  $18.5 \,\mu\text{m} \times 18.5 \,\mu\text{m}$  was too large for economical mass production. The Samsung's group succeeded in providing a  $9 \,\mu\text{m} \times 9 \,\mu\text{m}$  pixel by implementing the DVS in a backside illuminated (BSI) sensor. This kind of sensor increases the pixel responsivity thanks to its flip of the metal structure upside-down [33]. Therefore, the light particles are not anymore blocked by routing layers. With this new design, capacitors of the SCA circuit can overlap the photodiode improving therefore the pixel area. The Samsung's group also succeeded in reaching a data rate of 300 Meps (mega event per second) by grouping several neighboring pixels and dealt with them like a single one, with ON and OFF events of the same pixels group processed in parallel.

#### 1.4.3 Summary

The features of the different neuromorphic architectures designed for sparse vision data acquisition are summarized in Table 1.1. After a discussion of some figures of merit, an image sensor is chosen to be the start point of this study.

**Technology:** Although charge-coupled devices (CCD) provide higher pixel sensitivity and lower noise images, all the state-of-the-art architectures were designed in CMOS technology in order to integrate analog and digital processing down to the pixel level. Moreover, as CCD required a special manufacturing process, they are more expensive than CMOS imagers [14, 20].

**Fill Factor and DR:** Recent studies as the DAVIS and the ATIS showed an increase of the fill factor and of the DR compared to their predecessors. The Samsung's pixel fill factor was not mentioned but is intended to be high as it uses a BSI photodiode.

Power consumption: The power consumption reached by the Barranco's work in 2011 is the higher one due to its preamplification stages. However, the definitions of a high and a low activity are not really standardized across the different studies. Barranco defined its low activity as moderate output event rates (below 1 Meps), the ATIS as no DVS activity, the DAVIS did not provide any scale and Samsung defined it as an output event rate of 100 Keps. A high activity was defined by Barranco as an output event rate above 1 Meps, by Samsung at 300 Meps and was not defined by the DAVIS and the ATIS. Older works did not give any of the two definitions. Hence, comparison in power consumption between the different sensors is not easy. A way to facilitate this comparison would be to have the DC power of each architecture as well as its required energy to produce an event.

Contrast sensitivity: Minimum contrast sensitivity is application dependent. Actually, a low contrast sensitivity sensor as the Barranco's imager in 2013 provides a more detailed information but at the price of a higher event rate. Hence, there is no good or poor contrast sensitivity.

**FPN:** The fixed pattern noise (FPN) represents the pixel to pixel variation. It was defined by Lichsteiner in its first DVS. According to it, FPN is calculated as the standard deviation of measured contrast threshold expressed in [%] of illumination change. A fixed pattern noise of 2.1 % was reported in its paper. The most recent works kept its definition. The Barranco's imager in 2011 showed an increased of the FPN due to its minimum latency improvement. In 2013, the sensor reached a lower FPN while still decreasing the minimum latency. The ATIS's pixel succeeded to reach a FPN below 0.25% thanks to the implementation of a correlated double sampling method. Finally, compared to the ATIS, the DAVIS's pixel showed an increase of the FPN (3.5%).

Minimum latency: The minimum latency is determined by the time taking by the first event to occur when the pixel is excited with a step photocurrent change of 30% at 1 klx. Excepted for the ATIS, each time a new architecture is proposed, it presents a decrease of this feature.

As the Zaghloul's architecture aimed more to provide a pixel based on the retina key features than create a practical design, its poor dynamic range and high power consumption make it not suitable for this study. Then, as mentioned before, the Mallik et al. pixel is also not appropriate for this work as its synchronous pixel does not reflect the asynchronous principles of operation of the human retina. Concerning the asynchronous pixels constructed in a mature 0.18 μm or 0.35 μm CMOS technology, the DAVIS is the one reaching the larger dynamic range, the lower minimum latency and the smaller pixel area while consuming only 0.32 μW/pixel at high activity. Moreover, it uses only 1 photodiode making it more suitable for high-speed applications than the ATIS. The Samsung's dynamic vision sensor succeeded to further decreases the pixel area to  $9x9 \mu m^2$  with a BSI sensor designed in 90 nm CMOS technology. As a 0.18 µm CMOS technology is preferred to integrate our work to the DVS developed in UCL, this study starts from the DAVIS to develop its own pixel architecture. More precisely, it starts from the DVS part of the DAVIS as this work aims to provide only a pixel detecting changes in light intensity in order to decrease data-processing requirements. Asynchronous absolute light information could be detected in a future work by integrating our pixel to the DVS from UCL.

Table 1.1 – Summary of state-of-the-art architectures.

|                   | Samsung [32]         | DAVIS [5]            | ATIS [6]             | Barranco<br>2013 [27] | Barranco<br>2011 [30] | Lichsteiner [7]      | Mallik [26]         | Zaghloul [24]        |

|-------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|----------------------|---------------------|----------------------|

| D 4: 1:4          | DVS                  | DVG + ADG            | DVS +                | DVS                   | DVS                   | A 1                  | ADC:                | Α1                   |

| Functionality     | DVS                  | DVS + APS            |                      | DVS                   | DVS                   | Asynchronous         | APS imager          | Asyn. spatial        |

|                   |                      |                      | Exposure             |                       |                       | temporal             | + temporal          | and temporal         |

|                   |                      |                      | measurements         |                       |                       | contrast             | change detection    | contrast             |

| CMOS              | 90 nm CIS            | $0.18 \ \mu m \ CIS$ | 0.18 μm CIS          | $0.35 \ \mu m \ CIS$  | $0.35~\mu m~CIS$      | $0.35 \ \mu m \ CIS$ | $0.5 \ \mu m \ CIS$ | $0.35 \ \mu m \ CIS$ |

| Technology        | 1P5M BSI             | 1P6M MIM             | 1P6M MIM             | 2P4M                  | 2P4M                  | 2P4M                 | 2P3M                | 2P4M                 |

| Chip size $mm^2$  | 8 x 5.8              | 5 x 5                | 9.9 x 8.2            | $4.9 \times 4.9$      | $5.5 \times 5.6$      | 6 x 6.3              | 3 x 3               | $3.5 \times 3.5$     |

| Array size        | 640 x 480            | 240 x 180            | 304 x 240            | 128 x 128             | 128 x 128             | 128 x 128            | 90 x 90             | 96 x 60              |

| Pixel size $um^2$ | 9 x 9                | 18.5 x 18.5          | 30 x 30              | 30 x 31               | 35 x 35               | 40 x 40              | 25 x 25             | 34 x 40              |

| Fill factor       | N.A.                 | 22%                  | 30%                  | 10.5%                 | 8.7%                  | 8.1%                 | 17%                 | 14%                  |

| Pixel complexity  | N.A.                 | 47 T.                | 77 T.                | N.A.                  | N.A.                  | 26T.                 | 6T.                 | 38T.                 |

|                   |                      | 1 photodiode         | 2 photodiodes        |                       |                       |                      |                     |                      |

| Supply voltage    | 2.8V analog          | 1.8V/3.3V            | 3.3V analog          | 3.3V                  | 3.3V                  | 3.3V                 | 5V                  | 3.3V                 |

|                   | 1.2V digital         | ,                    | 1.8V digital         |                       |                       |                      |                     |                      |

| Power             |                      |                      |                      |                       |                       |                      |                     |                      |

| high activity     | 50 mW                | 14 mW                | 175 mW               | 4  mW                 | 231 mW                | 24 mW                | 30 mW               | 62.5 mW              |

| low activity      | 27 mW                | 5 mW                 | 50 mW                |                       | 132 mW                |                      |                     |                      |

| Power/pixel       |                      |                      |                      |                       |                       |                      |                     |                      |

| high activity     | $0.16~\mu\mathrm{W}$ | $0.32~\mu\mathrm{W}$ | $2.4 \mu W$          | $0.24~\mu\mathrm{W}$  | $14.1~\mu\mathrm{W}$  | $1.46~\mu\mathrm{W}$ | $3.7 \mu W$         | $10.85 \ \mu W$      |

| low activity      | $0.088~\mu{ m W}$    | $0.12~\mu\mathrm{W}$ | $0.69~\mu\mathrm{W}$ |                       | $8.06~\mu\mathrm{W}$  |                      |                     |                      |

| DR                | N.A.                 | 130dB DVS            | 125dB                | 120dB                 | 100dB                 | 120 dB               | 51dB                | 50dB                 |

|                   |                      | 51dB APS             |                      |                       |                       |                      |                     |                      |

| Min. contrast     | 9%                   | 11%                  | 30% @ 1klux          | 1.5%                  | 10%                   | 15%                  | 2.1%                | N.A.                 |

| sensitivity       |                      |                      |                      |                       |                       |                      |                     |                      |

| FPN               | N.A.                 | 0.5% APS             | <0.25%               | 0.9% DVS              | 4%                    | 2.1%                 | 0.5%                | N.A.                 |

|                   |                      | 3.5% DVS             | intensity            |                       |                       |                      |                     |                      |

| Min. latency      | N.A.                 | 3us                  | <4us                 | 3.2us                 | 3.6us                 | 15us                 | N.A.                | 10Meps               |

|                   |                      | @ 1klux              | @ 1klux              | @ 2klux               | @ 25klux              | @ 1klux              |                     | _                    |

## Pixel architecture and specifications

| Contents |                                |  |  |  |  |  |  |  |

|----------|--------------------------------|--|--|--|--|--|--|--|

| 2.1      | Pixel architecture             |  |  |  |  |  |  |  |

| 2.2      | Principles of operation        |  |  |  |  |  |  |  |

| 2.3      | Photoreceptor circuit          |  |  |  |  |  |  |  |

|          | 2.3.1 Photodiode               |  |  |  |  |  |  |  |

|          | 2.3.2 Photoreceptor transistor |  |  |  |  |  |  |  |

|          | 2.3.3 Bias point               |  |  |  |  |  |  |  |

| 2.4      | Switched capacitor amplifier   |  |  |  |  |  |  |  |

|          | 2.4.1 Capacitors               |  |  |  |  |  |  |  |

|          | 2.4.2 Amplifier                |  |  |  |  |  |  |  |

|          | 2.4.3 Switch                   |  |  |  |  |  |  |  |

| 2.5      | Comparators                    |  |  |  |  |  |  |  |

| 2.6      | Logic                          |  |  |  |  |  |  |  |

This second chapter aims to describe the pixel architecture chosen in this study to implement a neuromorphic CMOS imager. Firstly, the pixel architecture is presented and its similarities and differences with DAVIS pixel are highlighted. Then, the pixel principles of operation are explained. Finally, based on the pixel study, some pixel design guidelines are given. This chapter is intended to be independent of any technology as its main goal is to provide guidelines for the pixel design. Hence, exporting the pixel architecture in any technology is facilitated.

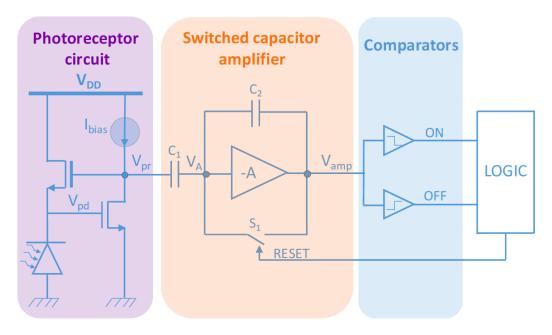

#### 2.1 Pixel architecture

The pixel architecture studied in this Master Thesis is a modified version of the state-of-the-art architecture DAVIS. It is represented in Figure 2.1.

FIGURE 2.1 – Schema of the pixel architecture studied in this Master Thesis.

Therefore, the architecture is composed of four circuits:

- Photoreceptor circuit: it is responsible for the logarithmic transduction from the sensed light to its output voltage  $V_{pr}$ . The bias voltage  $V_{pd}$  allows to keep the photodiode at virtual ground.

- Switched capacitor amplifier: it amplifies the change in photocurrent intensity since the last reset. Its output is noted  $V_{amp}$ .

- Comparators: it compares the output of the switched capacitor amplifier with two thresholds. If the upper threshold is reached, the corresponding comparator produces an OFF event. On the other side, if the lower threshold is reached, the corresponding comparator produces an ON event.

- Logic: when an event is produced, the logic circuit provides the signal needed to reset the switched capacitor amplifier circuit.

Compared to the DAVIS pixel, this study does not contain any buffer circuit as it is not required by the architecture. The addition of a buffer increases indeed the pixel area and decrease its performances as it is discussed in Section 3.3. Then, as the subject of this study is focused on the neuromorphic pixel either than on the sensor itself, the AER logic is replaced with a simple logic providing the reset signal. The AER logic can still be easily added later with additional eleven transistors and one capacitor [7]. Another significant difference resides in the lack of an active pixel sensor part. Actually, this study is focused only on relative changes in light intensity. However, a possible solution to synchronously

produce absolute light information is to integrate the dynamic pixel sensor (DPS) from UCL (see Annexe A.1) to the DVS developed in this Master Thesis. Finally, each ideal bloc presented in the schematic view is realized apart from the ones used in the DAVIS, the purpose being to target three figures of merit: a low power consumption, a high dynamic range and a low pixel area. Hence, this work is only inspired by the schematic architecture of the DAVIS and not from its implementation.

To understand more deeply the pixel behavior, its principles of operation are analyzed in the next section. Afterwards, the four pixel circuits are studied and some of their specifications and architectural choices are introduced. These specifications are intended to be independent of any technology, the main purpose being to give some guidelines to respect during the pixel design. Obviously, the pixel area minimization by using as much as possible small transistor size is a guideline available for all circuit blocks.

#### 2.2 Principles of operation

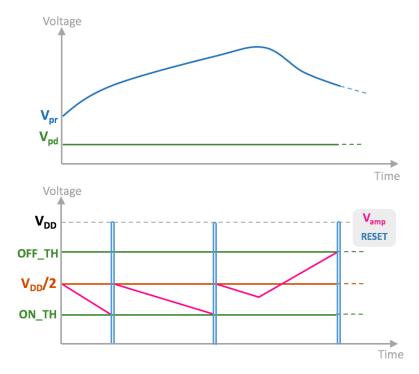

The ideal pixel behavior is represented in FIGURE 2.2. In the upper graph, the photoreceptor circuit output as well as the photodiode bias voltage are represented. Depending on the sensed light intensity, the voltage  $V_{pr}$  has a logarithmic variation. The bias voltage  $V_{pd}$  stays constant over time. In the lower graph, the output voltage of the switched amplifier capacitor circuit as well as the reset signal and the two levels of thresholds are drawn. When the voltage  $V_{pr}$  is rising, the output voltage  $V_{amp}$  decreases due to the negative gain of the switched capacitor amplifier. The SCA output voltage follows then the inverse variation of  $V_{pr}$ . When it reaches a threshold, the logic circuit performs a reset of  $V_{amp}$  to  $V_{DD}/2$ .

Figure 2.2 – Pixel principles of operation.

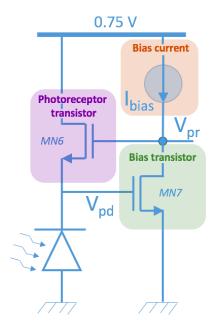

# 2.3 Photoreceptor circuit

The photoreceptor circuit, responsible for the transduction from the absorbed light to an electrical signal, is the first circuit block of the pixel. Firstly, the photoreceptor circuit is composed of a photodiode that sensed the photons and converts them to a photocurrent. The choice of this photodiode is important as it defines the pixel responsivity. Then, the transistor located above the photodiode performs the logarithmic conversion between the sensed light and its gate voltage  $V_{pr}$ . This transistor is called the *photoreceptor transistor* for the rest of this study. Finally, a bias source and its transistor (called the bias transistor) allow to keep the photodiode at a virtual ground. Guidelines to choose these different elements are given in the next sections, starting with the photodiode.

#### 2.3.1 Photodiode

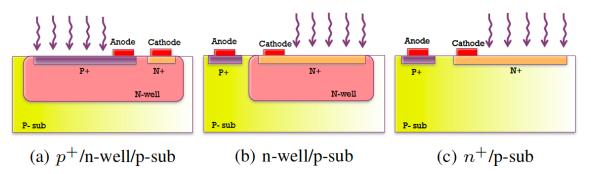

Performance parameters of a CMOS compatible photodiode vary according to the photodiode size, geometry and type. The three available CMOS compatible types of photodiode are the  $n^+$ /p-sub, the n-well/p-sub and the  $p^+$ /n-well/p-sub types. The cross section of each of them is represented in Figure 2.3.

FIGURE 2.3 – Cross section of the photodiode types (from [34]).

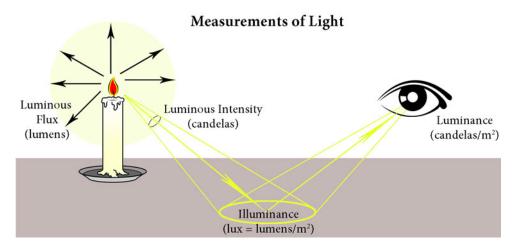

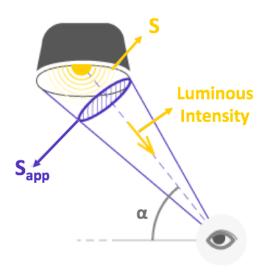

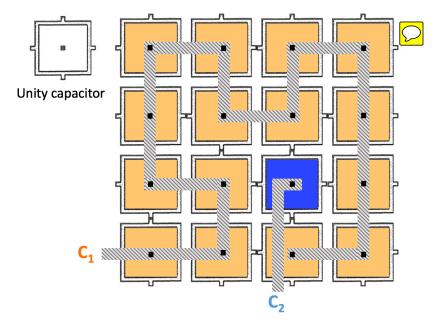

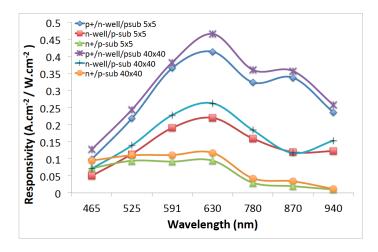

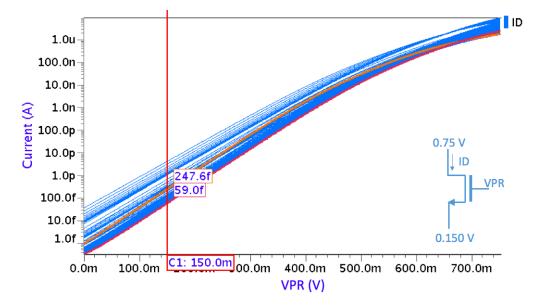

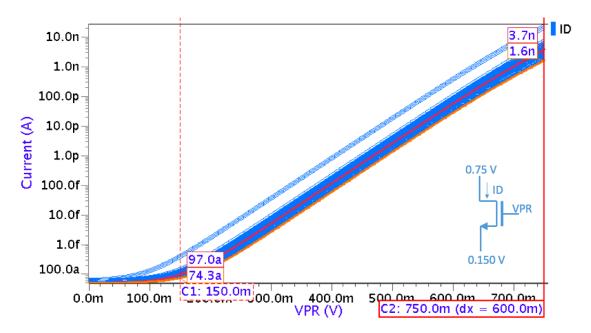

The photodiode type choice is important as it determines different figures of merit of the pixel as its responsivity and its fill factor. In order to select the most adapted one, the three types are presented and compared hereunder. Moreover, their different figures of merit are discussed [19, 34].