#### Verification of railway interlocking systems

Quentin Cappart

Thesis confirmation step

Institute of Information and Communication Technologies, Electronics and Applied Mathematics (ICTEAM) Louvain School of Engineering (EPL) Université catholique de Louvain (UCL)

> Louvain-la-Neuve Belgium

Examining board

Prof. Pierre Schaus, Supervisor Prof. Yves Deville Prof. Charles Pecheur Prof. Axel Legay UCL/ICTM, Belgium UCL/ICTM, Belgium UCL/ICTM, Belgium INRIA, France

### Abstract

A railway interlocking is the system ensuring a safe train traffic inside a station by monitoring and controlling signalling components such as the signals or the points. Modern interlockings are controlled by a generic software that uses data, called application data, reflecting the layout of the station under control and defining which actions the interlocking can perform. The safety of the train traffic relies thereby on application data correctness, errors inside them can lead to unexpected events, such as collisions or derailments. However, the application data are nowadays prepared by automatic tools that do not guarantee a sufficient level of safety. Furthermore, their verification is a time consuming task and error prone as it is mostly performed by human testers. Given the high level of safety required by such a system, verification of application data is a critical concern. For such reasons, automatising and improving the verification process of application data is an active field of research. Most of this research is based on model checking, which performs an exhaustive verification of the system but which suffers from scalability issues because of the state space explosion problem.

In this thesis, we investigate new verification methods aiming to deal with this problem. More concretely, we introduce methods such as random simulation, statistical model checking and dedicated algorithm that were until now never applied for verifying interlocking systems. The relevance and performance of these methods are also analysed through different realistic stations of the Belgian railway network. ii

## Acknowledgements

This research is financed by the Walloon Region as part of the Logistics in Wallonia competitiveness pole.

iv

### Foreword

Railway operators are faced with competition from road, air and maritime transport. They need to improve in terms of the globalisation of traffic and the interoperability between operations and infrastructure which are more complex than in other modes. To deal with this issue, Walloon Region of Belgium initiated in April 2014 INOGRAMS project. The main goal of this project is to maintain the competiveness of Wallonia's railway industry in the face of other transportation means. Given the large scope of this project, it is divided into seven work package.

I do my thesis in the context of this project. More specifically, I work on the first work package. Its goal is to propose innovative solutions for easing the future development of new interlocking systems. As the development of such systems must follow the highest safety requirements, the same rules must apply for our solutions. For this project, I collaborate with several companies and universities such as Alstom, Cetic, UMons and UNamur. Together we develop a tool which can be used to automatically generate a new kind of application data and verify their correctness. By correct we mean that it will never cause any safety of availability issue. My main contribution is related to the verification part. I investigate how the verification can be performed through different methods. vi

### Contents

| 1        | Intr | oduction                                                              | 1         |

|----------|------|-----------------------------------------------------------------------|-----------|

|          | 1.1  | Research goals                                                        | 1         |

|          | 1.2  | Overview of the contributions                                         | 2         |

|          | 1.3  | Publications                                                          | 4         |

|          | 1.4  | Outline                                                               | 5         |

| <b>2</b> | Inte | prlocking principles                                                  | 7         |

|          | 2.1  | Context                                                               | 7         |

|          | 2.2  | Components of an interlocking                                         | 10        |

|          | 2.3  | Solid State Interlocking                                              | 12        |

|          | 2.4  | Interlocking behaviour in SSI                                         | 15        |

|          | 2.5  | Station topology in railML                                            | 18        |

|          | 2.6  | Case studies                                                          | 21        |

|          |      | 2.6.1 Station of Namêche                                              | 22        |

|          |      | 2.6.2 Station of Braine l'Alleud                                      | 22        |

|          |      | 2.6.3 Station of Courtrai                                             | 23        |

| 3        | Moo  | del of an interlocking system                                         | <b>25</b> |

|          | 3.1  | General approach                                                      | 25        |

|          | 3.2  | SSI translator                                                        | 26        |

|          | 3.3  | railML+ translator                                                    | 28        |

|          | 3.4  | Interlocking model                                                    | 29        |

|          | 3.5  | Train model                                                           | 31        |

|          | 3.6  | Signalman model                                                       | 32        |

|          | 3.7  | Simulator                                                             | 32        |

|          |      | 3.7.1 Simulation taxonomy $\ldots \ldots \ldots \ldots \ldots \ldots$ | 33        |

|          |                          | 3.7.2    | Principles of discrete event simulation                            |   |   |   |   |    |   |   | 35 |

|----------|--------------------------|----------|--------------------------------------------------------------------|---|---|---|---|----|---|---|----|

|          |                          | 3.7.3    | Simulator architecture                                             | • | • | • | • | •  | • | • | 38 |

| <b>4</b> | 4 Automatic verification |          |                                                                    |   |   |   |   | 45 |   |   |    |

|          | 4.1                      | Motiva   | ation                                                              |   |   |   |   |    |   |   | 45 |

|          | 4.2                      | Definit  | tion of requirements                                               |   |   |   |   |    |   |   | 46 |

|          |                          | 4.2.1    | Safety properties                                                  |   |   |   |   |    |   |   | 47 |

|          |                          | 4.2.2    | Availability properties                                            |   |   |   |   |    |   |   | 49 |

|          | 4.3                      | Applic   | ation data errors                                                  |   |   |   |   |    |   |   | 49 |

|          | 4.4                      | Model    | checking                                                           |   |   |   |   |    |   |   | 50 |

|          | 4.5                      | Rando    | m simulation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |   |   |   |   |    |   |   | 53 |

|          | 4.6                      | Statist  | ical model checking                                                |   |   |   |   |    |   |   | 55 |

|          |                          | 4.6.1    | Monte Carlo estimation                                             |   |   |   |   |    |   |   | 56 |

|          |                          | 4.6.2    | Bound choice                                                       |   |   |   |   |    |   |   | 58 |

|          |                          | 4.6.3    | Number of simulations                                              |   |   |   |   |    |   |   | 59 |

|          |                          | 4.6.4    | Parallelisation                                                    |   |   |   |   |    |   |   | 60 |

|          |                          | 4.6.5    | Covering tests                                                     |   |   |   |   |    |   |   | 61 |

|          |                          | 4.6.6    | Importance splitting                                               |   |   |   |   |    |   |   | 63 |

|          |                          | 4.6.7    | Experiments                                                        |   |   |   |   | •  |   | • | 65 |

|          | 4.7                      | Dedica   | ted algorithm                                                      |   |   |   |   |    |   | • | 68 |

|          |                          | 4.7.1    | Motivation                                                         |   |   |   |   |    |   |   | 68 |

|          |                          | 4.7.2    | Verification                                                       |   |   |   |   |    |   |   | 68 |

|          |                          | 4.7.3    | Experiments                                                        |   |   |   |   |    |   |   | 73 |

|          | 4.8                      | Relate   | d work                                                             | • | • | • | • | •  | • | • | 74 |

| 5        | Ver                      | ificatio | n toolbox                                                          |   |   |   |   |    |   |   | 77 |

| 6        | Con                      | clusio   | n                                                                  |   |   |   |   |    |   |   | 79 |

|          | 6.1                      | Contri   | bution of this thesis                                              |   |   |   |   |    |   |   | 79 |

|          | 6.2                      | Perspe   | ectives                                                            | • | • |   | • | •  |   | • | 80 |

| Bi       | bliog                    | graphy   |                                                                    |   |   |   |   |    |   |   | 83 |

# Chapter 1 Introduction

#### 1.1 Research goals

In the railway domain, an interlocking is the subsystem that is responsible for ensuring a safe and fluid train traffic by controlling active track components of a station. Among these components, there are the signals, defining when trains can move, and the points, that guide trains from track to track. Modern interlockings are computerised systems composed of a generic software taking as input data, called application data, describing the actions that the interlocking must take for each situation that can occur in a particular station [1]. The main requirement to consider when designing an interlocking is the safety. A correct interlocking must never allow critical situations such as derailments or collisions. To this purpose, an interlocking must satisfy the highest safety integrity level as stated by Standard EN 50128 of CENELEC [2]. Although the generic software is developed in accordance with these requirements, the reliability of an interlocking is also dependent of the correctness of its application data which are particular to each station. However, preparation of application data is still nowadays done by tools that do not guarantee the required level of safety. Beyond the safety, an interlocking must also ensure that no train will be stopped too long in the station in order to maintain the availability of the station. It is why availability, or fluidity, properties must also be considered. Most of the time, the verification of the application data, as well as its validation, is performed through testing on a physic simulator that reproduces the environment of the interlocking. This process is thus costly and error prone. Moreover manual testing does not cover all the scenarios that could possibly end-up in a unsafe situation.

To overcome this lack, research has been carried out in order to

improve the verification of the application data correctness. Most of it is based on model checking [3]. The goal is to perform an exhaustive verification of the system. It is done in three steps. First, the application data and the station layout are translated into a model reflecting the interlocking behaviour. Secondly, the requirements that the interlocking must ensure in order to prevent any issue are formalised. Finally, the model checker verifies that no reachable state of the model violates the requirements. The main advantage of this method is its exhaustiveness, if a requirement is not satisfied, the model checker will always detect it. However, this method suffers from the state space explosion problem. The number of reachable states exponentially grows as the size of the model grows and the model checker algorithm might not return a result within a reasonable time in practice.

Verification of railway interlocking system is a critical concern. Moreover, without optimisation or specific improvements, model checking cannot be used for verifying large stations. The goal of my research is to improve this verification. For that, I investigate several methods in order design a new verification process which can be used for verifying stations of any size and which can be fully automated.

#### 1.2 Overview of the contributions

This section presents all the contributions that have been developed through this thesis. Their complete description will follow later in this document. The contributions can be classified into two different groups: contributions related to data analysis and contributions related to verification.

**Contributions related to data analysis and preprocessing** Different information such as the interlocking behaviour or the infrastructure are required to perform the verification. However, these information come from different data sources and have a format not directly exploitable. It is why one of the first tasks was to extract and analyse these data and to convert it into an adapted format. This group includes all the contributions related to the utility tools that we developed to perform

#### 1.2. OVERVIEW OF THE CONTRIBUTIONS

such tasks.

The first contribution is a tool designed to automatically parse application data expressed on Solid State Interlocking (SSI) format [4]. The output obtained can be used for several purposes and different kinds of modelling. For instance, it has been used in this thesis for designing a simulator of the interlocking behaviour. Furthermore, it has also been used in other works by Busard et al. [5] and Limbree et al. [6] in order to build a model which can be verified using different model checking methods.

Following the same idea, the second contribution is a parser tool extracting the topology of a station from a data source based on railML [7]. The simulator, as well as [5, 6] is also built using this translator.

**Contributions related to verification** This group includes the new verification methods that we introduced during this thesis. Our global contribution is a framework and a methodology allowing an user to automatically verify the correctness of an interlocking from its application data and the topology of its station. Several contributions related to different parts of the framework have been realised:

- A model instancing the behaviour of the application data and the topology of a particular station. The model presented here is designed in order to allow its simulation by a discrete event simulator and its verification using Bounded Linear Temporal Logic (BLTL).

- The formalisation of the safety properties defined by Busard et al. [5] in BLTL. Such a logic is used in order to have the possibility to determine when the simulator must stop its processing.

- The introduction of an availability property that an interlocking must face in order to ensure that no train would be stuck in a station. Such a property has also been formalised in BLTL.

- A Discrete Event Simulation (DES) engine which can be run on the top of the previous model. This tool contains several advanced features such as the possibility to stop a simulation at any state and

to replay it later. A command line interface as well as a graphical user interface have also been developed in order to facilitate its utilisation and its visualisation.

- The utilisation of Statistical Model Checking (SMC) methods such ad Monte Carlo estimation, Chernoff's bound and importance splitting algorithm, in order to verify the model running with the simulator engine.

- A polynomial dedicated algorithm verifying that an interlocking will never cause derailments or collisions provided that an assumption of monotonicity hold. It can also verify that each train will reach the correct destination.

- An executable tool instantiating the model, its simulation, the requirements and the different verification methods.

#### 1.3 Publications

The work and methods presented on this thesis have already been presented in several publications:

- A first version of the model and its verification with a discrete event simulation approach have been published and presented at 29th European Simulation and Modelling Conference in October 2015 [8]. This paper describes how an interlocking can be verified using a random discrete event simulation and what is the interest of this approach compared to classical model checking approaches.

- **[UPDATE IF ACCEPTED]** An extended version of the model and its verification by statistical model checking have been submitted at *Formal aspect of computing* Journal. This paper deals with the drawbacks of [8] and improves the verification thanks to statistical model checking methods.

- [UPDATE IF ACCEPTED] Another extension of the model has been performed. Concretely, we added the bidirectional locking mechanism and the differentiation between a route command and a route activation. Furthermore, a polynomial dedicated algorithm verifying that the interlocking will never cause any safety issue

provided that some assumptions hold have been introduced. This work has been submitted at 35th International Conference on Computer Safety, Reliability and Security in September 2016.

#### 1.4 Outline

With the exception of the introduction, the content of this thesis is divided into five other chapters. They are organised as follows:

- Chapter 2 gives the background related to the railway interlocking domain on which this thesis is based. The structure of an interlocking, its behaviour, its input data and how signalling engineers can use it are described inside. Three case studies exploited in this work are also introduced.

- Chapter 3 presents how we modelled an interlocking system. The architecture of the model, its performances, its limitations and the hypothesis done are detailed.

- Chapter 4 deals with the verification of an interlocking system. First, the intrinsic difficulties of an automatic verification are stated. The state of the art methods dealing these issues, as well as their limitations, are then described. After that, new verification methods not yet used for interlocking are introduced and analysed. Finally, a toolbox taking over the verification methods developed through this thesis is presented.

- Chapter 5 presents the software implemented during this thesis. This software encompasses the different methods, principles and algorithms presented in this document.

Finally, the last chapter summarises the work done through this thesis and sketches possibilities of future work.

CHAPTER 1. INTRODUCTION

# Chapter 2 Interlocking principles

#### 2.1 Context

A railway interlocking is an arrangement of systems that prevents conflicting train movements in a station. It is more specially a signalling subsystem that controls physical components of a station before allowing a train through the station. To do so, the interlocking collect information about the occupation of the track layout and about the movable elements such as the points. It then evaluates this information and can permit or refuse train movements by setting signals on a proceed or a stop state.

Basically, an interlocking has three main functions which can be split into three levels [1]:

- **Operational level**: it includes the interface between the human signaller performing the request and the machine.

- **Interlocking level**: it includes the functions required to decide if the request performed by the signaller can be accepted or not, and to do the proper actions consequently.

- Element control level: it mainly includes the functions required to transmit information between the components.

Over the years, the progression of interlocking technology has not stopped to grow up. Existing technologies can be categorized into four groups:

• Human interlocking: all the functions (performing the request, checking its satisfiability and moving components) are performed by a human. It is the oldest mechanism for an interlocking.

- Mechanical interlocking: the signaller controls the interlocking through mechanical levers which are connected with each other. Information transmission to the physical components is done by wires.

- Electric interlocking: the signaller controls the interlocking through electric buttons. The physical components are controlled electrically through a relay technology.

- **Computer based interlocking**: it is the technology that is currently mostly used in the world. It is also called electronic interlocking. All the functions are performed electronically through a computer hardware and software.

Table 2.1 recaps the four forms of interlocking technologies and how the three functions are performed.

|            | operational       | interlocking  | element control |

|------------|-------------------|---------------|-----------------|

| human      | -                 | human         | human           |

| mechanical | mechanical levers | lever frame   | wires           |

| electric   | electric buttons  | relays        | electric        |

| electronic | monitor/keyboard  | hard/software | electronic      |

**Table 2.1.** Interlocking technologies and technical application of the functions in the three levels [1].

This thesis deals with computer based interlockings. Such interlockings are controlled by a generic software that uses data, called **application data**, reflecting the layout of the station under control and defining which actions the interlocking can perform. The safety, implying that no accident will occur, is the most important aspect to consider when designing an interlocking. For this reason, European Railway Agency has edited strict safety norms in an effort to harmonize the signalling principles and rules at the European level [2, 9]. Although the generic software is developed in accordance with these requirements, the safety of the train traffic relies also on the correctness of the application data.

Currently, the application data are prepared manually and are thus subject to human errors. For example, some prerequisites to the clearance of the home signal of a route can be missing. This kind of error can easily be discovered by a code review or a static analysis [10]. However, errors caused by concurrent actions, like route commands, are much harder to spot. In this case, the combination of possible concurrent actions explodes quickly and testing manually all the combinations is impracticable. As testing all the possible scenarios is impossible, the manual validation of the application data relies on a relaxed verification process performed on three steps:

- 1. **Functional tests**: they ensure that the system responds properly to the commands issued by the controller. Those tests are performed by the expert who wrote the application data.

- 2. Safety tests: they check that each command is tested and that all the conditions that are supposed to impact the command are tested in all their possible values. Those tests are prepared and carried out by an independent tester.

- 3. **Reviewing**: the application data are finally reviewed by the engineer in charge of the project.

During this process, all the anomalies are traced in a bug management tool and must be fixed before the interlocking is commissioned. This validation is mainly done manually through a physic simulator that reproduces the behaviour of the interlocking on real infrastructures. In addition to the high cost of this process, it is also error prone because there is no guarantee that all the situations that could end-up in a safety issue have been tested by the simulator.

Generally speaking, the interlocking must known which actions can be done and under which conditions. Such information can be defined in different ways according to the type of interlocking considered. Since 1992, Belgian railway stations have used SSI format [4] for their interlockings. Such interlockings use a **route based paradigm**. A route is the path that a train is supposed to follow inside a station. When a train is entering in a station, a signalman assigns a route to the train by performing a route request. The interlocking will process the request, decide if it can be accepted and perform then some actions in order to set it. The rest of this section states the components used by a route based interlocking, presents how they are formalised in SSI, explains their behaviour and illustrates it on a case study.

#### 2.2 Components of an interlocking

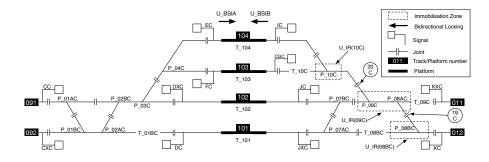

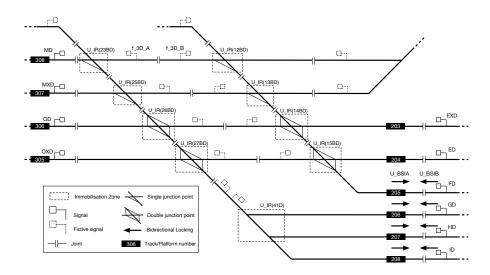

Let us first present our case study: Braine l'Alleud Station. A representation of its topology with its related components is shown in Figure 2.1.

Figure 2.1. Layout of Braine l'Alleud Station.

This figure recaps the component types that are used in our model. On the one hand, there are the **physical components** of the track layout:

- The **tracks** (e.g Track 101) are the railway structure where trains can move. A track can be a **platform** if the trains can stop on it in order to pick up passengers.

- The **track segments** (e.g T\_01BC) are the portions of tracks where the trains can be detected. They are delimited by the **joints**.

- The **points** (e.g. **P\_01AC**) are the movable devices that allow trains to move from one track to another. According to Belgian convention, they can be in a normal position (left) or in a reverse position (right). They are also called railway switches.

- The signals (e.g. S\_CXC or simply CXC) are the devices used to control the train traffic. They are set on a proceed state (green)

if a train can safely move into the station or in a stop state (red) otherwise.

Braine l'Alleud Station is composed of 4 tracks, 17 track segments, 12 points and 12 signals. The physical components are controlled and monitored by a single interlocking. For instance, the system can detect that a train is waiting on Track segment  $T_01AC$  in front of Signal CC and then puts this signal on a proceed state if this action will not cause any safety issue.

On the other hand, there are the **logical components**. As previously said, a **route** is the path that a train is supposed to follow inside a station. It is generally named according to its origin and its destination place. Signals are often used as references for the origins whereas tracks or platforms are used for destinations. For instance, Route R\_CXC\_101 starts from Signal CXC and ends on Platform 101. When a train is approaching to a station, a signalman performs a route request to the interlocking in order to ask if the route can be commanded. It is a route command. If the request is fulfilled, all the requested components are locked but the train cannot use the route yet because the start signal is still on a stop state. The start signal goes to a proceed state only after the activation of the route. **Route activations** are periodically tried by the interlocking after that the route has been commanded. Once the route activation has been accepted, the train can finally use the route. The interlocking handles such requests and accepts or rejects it according to the station state. To manage the requests, logical components are used:

- The **subroutes** are the contiguous segments that the trains must follow inside a route. When a route is commanded for a train, a set of subroutes is locked. When not requested, subroutes are in a free state.

- The **immobilisation zones** are the variables materialising the immobilisation of a set of points. When they are locked, their attached points cannot be moved. For instance, Immobilisation zone U\_IR(09C) prevents Points P\_08AC and P\_09C to be commanded.

- The **bidirectional locking** is the mechanism used to prevent head to head collisions on platforms. Each bidirectional locking

consists of two variables  $(U\_BSIA \text{ and } U\_BSIB)$  which can prevent the activation of a route coming from the left or the right of the platform. For instance, when  $U\_BSIA(104)$  is locked, no route going to Platform 104 from the right can be activated.

There are 32 possible routes in Braine l'Alleud. To manage it, 48 subroutes, 10 immobilisation zones and 4 bidirectional locking mechanisms are used.

#### 2.3 Solid State Interlocking

Solid State Interlocking (SSI) refers together to the first computer based interlocking systems, and to the software used to develop these systems. Its development started in the 1970s by British Railways in collaboration with GEC (now Alstom) and Westinghouse. It quickly becomes one of the most widely used interlocking systems, especially in Western Europe and countries of the British Commonwealth [1]. The software is structured into two parts:

- The **generic software** which serves as an interpreter for the application data and carries out system functions like communications. This part does not change from one station to another and can then be verified once and only once. The development and the validation of that generic software follow the highest safety rules applicable to the domain.

- The specific **application data** which express all interlocking functions. They are written in a data language designed to be used by signalling engineers. Unlike the generic software, the application data are specific to a station and must then be verified for each station considered.

The ability of the interlocking to avoid critical situations, like train collisions, relies on the safety level achieved by the combination of the generic software and of the application data. Application data describe then the behaviour of an interlocking system instantiated to a specific station. They are divided into several configuration files. Only some of them are considered in this work: • All the variables and structures used in the application data are declared in several .id files. Table 2.2 presents these variables with their possible values.

| Component             | SSI variable        | Possible values                        |

|-----------------------|---------------------|----------------------------------------|

| Subroute              | U_id                | f (free) / l (locked)                  |

| Immobilisation zone   | U_IR( <i>id</i> )   | f (free) / l (locked)                  |

| Bidirectional locking | U_BSIA( <i>id</i> ) | f (free) / l (locked)                  |

| Didirectional locking | U_BSIB( <i>id</i> ) | I (IIee) / I (IOcked)                  |

| Route                 | R_id                | s (set) / $xs$ (unset)                 |

| Point                 | $P_id$              | n (normal) / $r$ (reverse) +           |

| 1 01110               | 1_00                | cf / c / cd                            |

| Track segment         | $T_{id}$            | c (clear) / o (occupied)               |

| Signal                | S_id                | $\texttt{stop} \ / \ \texttt{proceed}$ |

Table 2.2. Variables with their possible values expressed in SSI format.

Each component has a unique identifier *id* and can have two values except for the points which encompass two information: a position (normal or reverse) and a status. The status refers to the life cycle of the points: free to be commanded (cf), commanded (c), and finally commanded and directed (cd). Their state is then an aggregation of both information. For instance, P\_01BC cdn means that Point P\_01BC has been commanded and directed to its normal position. Concerning the bidirectional locking, two variables are used for this mechanism. Les us define these components and their values with an EBNF syntax [11]:

| $\langle component \rangle$ | ::= Subroute   UIR   UBSIA   UBSIB  <br>Route   Point   Track_segment   Signal |

|-----------------------------|--------------------------------------------------------------------------------|

| $\langle value \rangle$     |                                                                                |

• **PRR.dat**: it defines the conditions that must be satisfied in order to accept a route request. The actions that the interlocking must perform when the request is accepted are also defined inside.

The instructions and expressions described in this file follows this grammar:

| $\langle PRR\_file \rangle$        | $::= \{\langle route\_request \rangle\}$                                                                                                           |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| $\langle route\_request \rangle$   | $::= \mathbf{Q^{*}(Route) if } \{ \langle condition \rangle \} \\ \mathbf{then} \{ \langle action \rangle \} [ \langle UBSI\_expression \rangle ]$ |

| $\langle UBSI\_expression \rangle$ | ::= if (UBSIA   UBSIB) f<br>then (UBSIA   UBSIB) 1                                                                                                 |

| $\langle condition \rangle$        | ::= $\langle component \rangle \langle value \rangle$                                                                                              |

| $\langle action \rangle$           | $::= \langle component \rangle \langle value \rangle$                                                                                              |

• **PFM.dat**: it defines the conditions that must be ensured before moving a point.

| $\langle PFM\_file \rangle$      | $::= \{\langle point\_request \rangle\}$                                                                                         |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| $\langle point\_request \rangle$ | $ ::= \operatorname{*Point} \mathbf{N} \langle condition \rangle \\ \operatorname{*Point} \mathbf{R} \langle condition \rangle $ |

• **FOP.dat**: it defines the necessary conditions for releasing logical components after they have been used.

| $\langle FOP\_file \rangle$         | $ ::= \{ \langle subroute\_release \rangle \mid \langle UIR\_release \rangle \mid \\ \langle UBSIA\_release \rangle \mid \langle UBSIB\_release \rangle \} $ |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\langle subroute\_release \rangle$ | ::= Subroute f if $\langle condition \rangle$                                                                                                                |

| $\langle UIR\_release \rangle$      | $::= if UIR   then if (condition) \\ then (action)$                                                                                                          |

| $\langle UBSIA\_release \rangle$ | ::= UBSIA f if $\langle condition \rangle$ |

|----------------------------------|--------------------------------------------|

| $\langle UBSIB\_release \rangle$ | ::= UBSIB f if $\langle condition \rangle$ |

• **OPT.dat**: generally speaking, it describes the life cycle of the routes from their command to their releasing. We use it to know when the start signal of a route can be set at a proceed state.

| $\langle OPT\_file \rangle$         | $::= \{\langle route\_activation \rangle\}$                                                                                          |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| $\langle route\_activation \rangle$ | $ ::= \ \mathbf{if} \ \langle condition \rangle \ \mathbf{then} \ \langle action \rangle \\ \mathbf{else} \ \langle action \rangle $ |

Let us mention that the grammars presented here only cover a subset of the application data. Indeed, for the sake of simplicity, we refined it in order to formalise only the elements used in our analysis. Detailed explanations about the components and the expressions are provided in the next sections. The other configuration files serve different purposes such as the communication between several interlockings and are not related to safety or availability.

#### 2.4 Interlocking behaviour in SSI

With both the physical and logical components, a route based interlocking controls the train traffic by monitoring the station, commanding routes, activating them, locking components and releasing them. In this section, we explain how a SSI interlocking manages these actions. All the possible actions and their underlying conditions are described in the application data. To illustrate the behaviour, let us consider the scenario where a train is coming from Track 012 and has to go to Platform 103 in Braine l'Alleud:

• Firstly, when the train is waiting at Signal KC, the interlocking will verify whether the request for Route R\_KC\_103 can be granted. Listing 2.1 presents the request according to the application data of Braine l'Alleud.

```

1

*Q_R(KC_103)

\mathbf{2}

if

R_KC_103 xs,

3

P_08BC cfr, P_08AC cfr, P_09C cfr,

4

P_10C cfn,

U_IR(08BC) f, U_IR(09C) f, U_IR(10C) f

5

R_KC_103 s,

6

then

7

P_08BC cr, P_08AC cr, P_09C cr,

8

P 10C cn,

9

U_IR(08BC) 1, U_IR(09C) 1, U_IR(10C) 1,

10

U_KC_19C 1, U_19C_20C 1, U_20C_CGC 1

```

Listing 2.1. Request for commanding Route R\_KC\_103.

The request is accepted only if Route R\_KC\_103 is not already set (line 2), if some points are free to be commanded to the reverse (cfr) or normal (cfn) position (lines 3-4) and if some immobilisation zones are not locked (line 5). If all the conditions are satisfied, R\_KC\_103 is set (line 6), the points are controlled to the requested position (lines 7-8) and some components like the immobilisation zones (line 9) or subroutes (line 10) are locked. At this step, Route R\_KC\_103 is set, or commanded, but not yet activated. Indeed, its start Signal KC is still on a stop state and the train can thereby not enter in the station yet.

• Before moving a point, the interlocking must verify that this action can safely be executed. Listing 2.2 illustrates such conditions for Point P\_08AC.

```

1 *P_08ACN U_IR(09C) f // N for normal position

2 *P_08ACR U_IR(09C) f // R for reverse position

```

Listing 2.2. Conditions allowing Point P\_08AC to move.

- Directly after the acceptance of the request described in Listing 2.1, the interlocking checks if a bidirectional locking must be used in order to prevent routes going to Platform 103 from the left to be activated. It is shown on Listing 2.3.

- 1 if U\_BSIA(103) f then U\_BSIB(103) 1

Listing 2.3. Bidirectional locking request for Platform 103.

• Once R\_KC\_103 has been commanded, the interlocking checks if it can safely activate the route and so gives the train an authority to move.

```

*R_KC_103

1

2

P_08BC cdr, P_08AC cdr, P_09C cdr,

if

3

P_10C cdn,

U_IR(08BC) 1, U_IR(09C) 1, U_IR(10C) 1,

4

5

T_08BC c, T_09C c, T_10C c, T_103 c,

6

U_BSIA(103) f

7

then

U_BSIB(103) 1,

8

S_KC proceed

```

Listing 2.4. Request for activating Route R\_KC\_103.

Listing 2.4 states that R\_KC\_103 can be activated only if the points are commanded and detected in the requested position (lines 2-3), if the immobilisation zones are thoroughly locked (line 4), if there is no train on some track segments (line 5) and if the bidirectional locking for trains coming from right to Platform 103 is free (line 6). The route activation results in locking the paired bidirectional locking (line 7) and in setting Signal S\_KC on a proceed state. At this step, the train can finally move into the station.

- When they are not used, locked components can be released. It is done according to the progress of the train on its route. After each train movement, the interlocking checks if a releasing event can be triggered. Listing 2.5 states the conditions for releasing Subroute U\_20C\_CGC. If all the conditions are fulfilled, the requested components are thoroughly released.

- 1 U\_20C\_CGC f if U\_KXC\_20C f, U\_19C\_20C f, T\_10C c

Listing 2.5. Conditions for releasing Subroute U\_20C\_CGC.

This process describes the life cycle of a route and how it is managed by the interlocking.

#### 2.5 Station topology in railML

The application data describe the behaviour of an interlocking applied to a specific station but contain no information about the track layout. However, the correctness of an interlocking is also related to its consistency with the track layout. It is why a reliable data source describing the track layout, or the **topology**, is necessary.

The topology can be encoded in different ways. A common approach is to represent it using a computer-aided design such as AutoCad [12]. Different information such as the track lengths or the geographic position of components can be described inside. It is the method currently used in Belgium. However, a graphical representation has some shortcomings. Given that the information is presented graphically, the processing of the schema and its integration into a verification model require manual works and can then hardly be automated.

Another way to represent the topology is to use a structured language. With this kind of representation, information can be automatically processed and used for different purposes. Based on a Extensible Markup Language (XML) structure, **railML** [7] is a markup language specialised for the railway domain. It was conceived to give a universal support for information which can be used for any applications related to the railway field. It is used by several companies such as Alstom, Siemens, Bombardier, Thales or Toshiba. As any markup language, railML is structured with schemas. There are gathered into four main schemas:

- **Infrastructure**: it describes the railway network topology and contains information about the physical components.

- **Timetable and Rostering**: it contains all the information about the timetables and the schedules.

- **Rolling stock**: it takes over all the information about the vehicles used (length, height, weight, etc.)

- **Common**: it encompasses the information not included in the other schemas.

#### 2.5. STATION TOPOLOGY IN RAILML

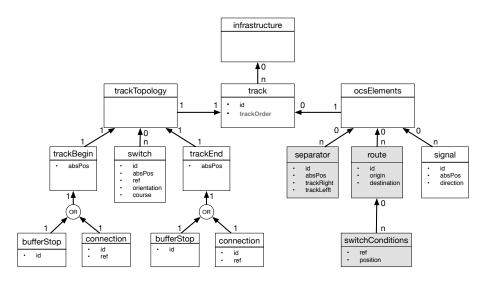

Only the infrastructure schema is related to the topology. However, railML does not provide yet all the information required to represent the whole topology. For instance, information such as the positions of joints are missing. To overcome this lack, we enriched railML with new elements. We call this extension **railML+**. Figure 2.2 summarizes the elements that we use from the infrastructure schema as well as their hierarchy. Explanation of the different schemas are provided thereafter.

Figure 2.2. railML infrastructure schema enriched with new elements (in grey).

- track An infrastructure has a set of tracks. Each of them is characterised by a unique identifier (id) and a relative position between the other tracks (trackOrder). In Braine l'Alleud, the track order varies from 0, for Track 101, to 3 for Track 104.

- **trackTopology** Each track has one and only one topology (1 to 1 relation). This subschema encompasses different physical components of the tracks.

- trackBegin It represents the beginning of a track. It is characterised by an absolute position (absPos).

- **trackEnd** It represents the end of a track. It is also characterised by an absolute position (absPos).

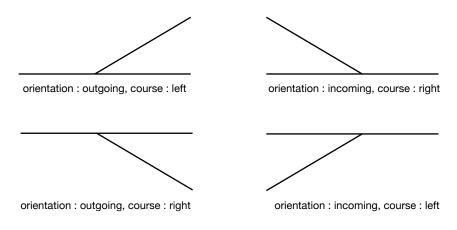

switch It represents the definition of a point. A trackTopology schema can have several points on it (0 to n relation). Each of them is characterised by a unique identifier, an absolute position, the identifier of its linked component (ref), and finally its physical disposition (orientation and course). Figure 2.3 presents the four possible dispositions of a point.

Figure 2.3. The fourth possible physical dispositions of a point.

For instance, Point P\_01BC as an incoming left disposition while Point P\_02AC has an outgoing left disposition.

- bufferStop It is one of the two possible extreme elements (trackBegin and trackEnd) for a track. It represents the border with another infrastructure. For instance, Braine l'Alleud has four bufferStop: two on the left of Signals CC and CXC and two on the right of KC and KXC. It is characterised by a unique identifier.

- connection It is the second possibility for a track extreme element. It models its connection with another component, typically a point. For instance, Track 103 is connected on the left with Point  $P_03C$  and on the right with Point  $P_09C$ .

- **ocsElements** This subschema encompasses several physical and logical components.

- signal It corresponds to the signals. They are characterised by a unique

identifier, an absolute position and a direction (up or down) defining the direction in which the signal must apply. In Figure 2.1, Signal CC is oriented upside whereas KXC is oriented downside.

- separator It corresponds to the joints. Each of them has a unique identifier, an absolute position and also the name of the track segment located at the left (trackLeft) of the joint and at its right (trackRight). This subschema, as well as the following, is not included in the basic version of railML but only in the extension railML+.

- route It correspond to a route as defined earlier. Each of them has an identifier, an origin (origin), and a destination (destination).

- switchConditions A route is also defined by the position of all the points crossed by the route in order to reach its destination. This subschema encompasses this information. It contains for each point, a reference (ref) to the points as defined in the switch schema, and their required position (position) in order to form the proper path from the origin of the route to its destination. For instance, Route R\_CXC\_102 requires Points P\_01BC, P\_02AC and P\_02BC to be set at the normal position and Point P\_03C to be set at the reverse position.

With these schemas, railML+ can thereby be used in order to specify the track layout of a station with more flexibility than the graphical approaches. It is why we propose here to use railML+ as a reference for the topology.

#### 2.6 Case studies

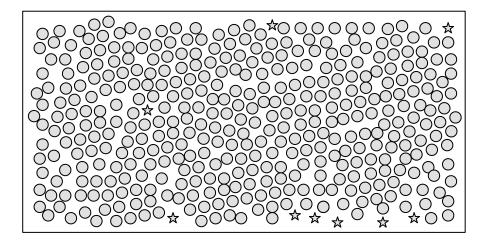

Three cases studies are analysed in this thesis: Braine l'Alleud Station, Namêche Station, and LK7 area of Courtrai Station. The choice of these case studies is not fortuitous. We chose stations of different size in order to have a realistic and broad overview of the different stations in Belgium. If the proposed methods can be applied on the three cases studies, they can theoretically also be applied for each Belgian station.

#### 2.6.1 Station of Namêche

Namêche is a Belgian city located near Namur in Wallonia. It has a small sized station composed of 4 tracks, 13 track segments, 7 points, 7 signals, 14 routes, 7 immobilisation zones and 26 subroutes. The bidirectional locking mechanism is not used in this station. The entire station is controlled by a single interlocking. A representation of its track layout is shown in Figure 2.4.

Figure 2.4. Layout of Namêche Station.

#### 2.6.2 Station of Braine l'Alleud

Already introduced in this document, Braine l'Alleud is a Belgian city located in the center of the country in Walloon Brabant Province. Its station is on the direct line (Line 124) between Charleroi and Brussels. It is a medium sized station composed of 4 tracks, 17 track segments, 12 points, 12 signals, 32 routes, 10 immobilisation zones, 48 subroutes and 4 bidirectional locking mechanisms. The entire station is also controlled by a single interlocking. A representation of its track layout is shown in Figure 2.1.

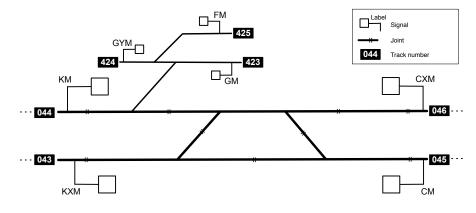

#### 2.6.3 Station of Courtrai

Courtrai, or Kortrijk, is a Belgian city located in the west of Belgium in Flanders. It is considered as a large station. The entire station is controlled by three interlockings that communicate together. Here, we are only interested in a subpart (LK7 Area) of Courtrai controlled by a single interlocking. A representation of the track layout of LK7 is shown in Figure 2.5.

Figure 2.5. Layout of LK7 area of Courtrai Station. [schema to be modified]

It is composed of 6 tracks, 19 track segments, 26 points, 24 signals, 70 routes, 9 immobilisation zones, 72 subroutes and 4 bidirectional locking mechanisms. Concerning the signals, 14 of them are fictive. A fictive signal is a signal that is not materialised in the track layout but that has a representation in the application data. Unlike Namêche and Braine l'Alleud, a route in Courtrai does not correspond to a complete itinerary for a train. When a train is entering into the station and must go to a particular destination, it is not done with one route but with a set of routes that must be commanded sequentially. For instance, if a train must go from  $S_ED$  to  $S_MD$ , two routes must be used sequentially, one from  $S_ED$  to  $S_f_3D_B$  and a second one from  $S_f_3D_A$  to  $S_MD$ . In

Courtrai, an itinerary is then a sequence of routes.

## Chapter 3 Model of an interlocking system

#### 3.1 General approach

The previous chapter described the principles of an interlocking system and how it is used to regulate the train traffic. It also introduced the problematic of application data verification and the lacks of the current situation in Belgium. This chapter presents how an interlocking system can be modelled and how its behaviour can be reproduced on a computer in order to automatically verify the application data correctness through several verification approaches. The structure of this chapter follows a top-down hierarchy. First, a global overview of the entire verification process is presented. Each step composing the approach is then separately detailed.

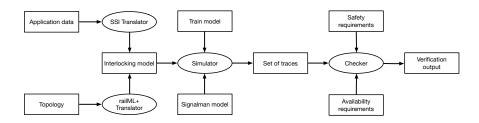

Our verification process is divided into several steps:

- 1. Generating a model of an interlocking by combining its application data and the track layout of its station. This is performed by two translators that parse and aggregate both data sources into a single model.

- 2. Creating a model representing a real train traffic in order to analyse how the interlocking model react to it.

- 3. Creating a model mimicking the actions that a human signalman can perform when trains arrive in the station.

- 4. Stating and formalising all the requirements that an interlocking system must satisfy in order to ensure a safe and fluid train traffic.

- 5. Reproducing the interlocking behaviour under a realistic train traffic. It is done through a simulator. A set of traces summarizing the different actions that occurred during the simulation as well as the states reached are then obtained.

- 6. Analysing the traces obtained and verifying that none of them contains states violating the requirements.

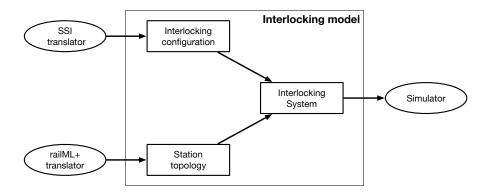

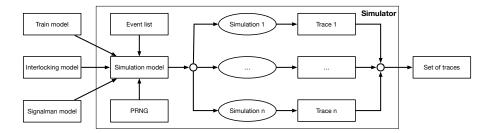

This entire process is gathered into a single framework implemented in Scala [13]. This language is multi-paradigm and supports the object oriented [14] and functional paradigm [15]. It is also compatible with Java language and its libraries [16]. The data flow diagram presented in Figure 3.1 resumes the main steps of the approach.

Figure 3.1. Step of the verification approach.

More details on the first steps are provided in the next sections. Steps related to verification are detailed in the next chapter.

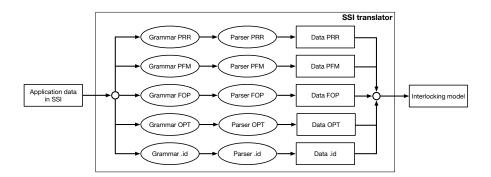

#### 3.2 SSI translator

The first step is to translate the input data into an exploitable format. This section is dedicated to the translation of SSI application data presented on Sections 2.3 and 2.4. As illustrated on Figure 3.2, the translation is done in two steps: the elaboration of grammars and the parsing.

**Grammar elaboration** Before translating the application data, grammars defining the format of the application must be specified. Such grammars are used by the parsing tool in order to capture the structure

Figure 3.2. SSI translator architecture.

of SSI language and then to know how it can be translated. As SSI data are described into several configuration files having each a particular, several grammars are required. The grammars used are presented in Section 2.3. According to Chomsky's hierarchy [17], such grammars are context-free [18].

**Definition 3.1** (Context free grammar). A context free grammar is a grammar where every production rule follows the pattern  $X \to \alpha$  where, X is a non terminal symbol and  $\alpha$  a sequence of terminal and/or non terminal symbols.

Context free grammars are often used for specifying programming languages because there exist efficient algorithms such as Early [19] or CYK [20] for their parsing. Furthermore, more efficient algorithms (Packrat [21], recursive descent [22], etc.) can be used provided that the considered grammar satisfies some other properties.

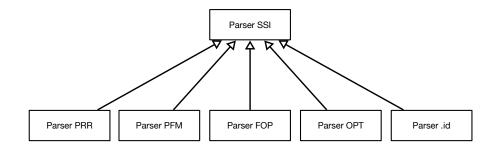

**Parsing** Once the grammars are specified, the next step is to use them for parsing the application data. Because several grammars are used, we designed a particular parser per grammar. However, some structures, as the the specification of a variable, have the same syntax in every file and are then common for every grammar. We use the inheritance mechanism [23] to take advantage of it. Figure 3.3 presents the inheritance diagram of our parser. Each parser is implemented as a class and inherits from **Parser SSI** which encompasses the common expressions of each file.

Furthermore, the parsers are designed to skip all the data non used in our model.

Figure 3.3. Inheritance diagram of the parser.

The parser uses a combinatory parsing technique [24]. It has been implemented using the combinator parser (util.parsing.combinator) package of Scala [25].

# 3.3 railML+ translator

As for the application data, the data related to the topology must also be translated in order to build the interlocking model. Its translation, illustrated in Figure 3.4, follows the same process.

Figure 3.4. railML translator architecture.

**Grammar elaboration** As presented in Section 2.5, the topology is expressed in railML+. Its grammar follows then an XML pattern. All the considered data are detailed in Figure 2.2.

**Parsing** There exist diverse algorithms for parsing XML data [26]. Our implementation is based on XML scala library (scala-xml) which

follows the standard SAX parser from Java library [27]. As output, the parser create a topology file which encompasses three information about the station:

- Characteristics about the physical components.

- How the physical components are connected together.

- All the possible routes in the station with their path determined by the position of the points.

# 3.4 Interlocking model

This section presents the structure of the interlocking model. Figure 3.5 gives an overview of it. Three components are involved: the configuration of the interlocking, the topology of the station, and the interlocking system itself. All of them are implemented as an object.

Figure 3.5. Architecture of an interlocking model.

**Interlocking configuration** This object is built from the parsing of the application data. It includes several attributes:

• A list for each kind of interlocking component (immobilisation zone, bidirectional locking, track segment and subroute). Each component is represented as an object with two attributes: a

unique identifier and its state, as presented in Table 2.2. The track segment objects include also a set of references of trains that occupy the segment.

• A syntax tree for each configuration file parsed. Such trees include all the information parsed that are required for the interlocking model.

**Station topology** This object is built from the parsing of the topology file. We model the station using graph theory [28]. Graph theory has already been deeply studied for modelling complex networks [29]. There are numerous examples of concrete applications as Internet [30], social networks [31] and transportation networks [32]. It has also been applied for railway signalling [33]. We model a station as an undirected graph. Points, signals, buffers stops and joints are represented by nodes and their connections by edges. Furthermore, each edge belongs to a particular track segment. The implementation is done using Jung library [34].

**Interlocking system** The interlocking system is only an aggregation of the two previous structures. It is used to reproduce the interlocking behaviour described in Section 2.4 and to apply it on the considered station. It is given as input for the simulator thereafter.

**Assumptions done** Furthermore the interlocking model is based on several assumptions:

- Signals can only have two states: stop and proceed.

- The start signals of routes move to the proceed state immediately after that the route has been activated.

- There is no distinction between a normal route and a shunting route. A shunting route is a route that the train can follow only with a low speed in order to join it with another train.

- All the physical components are perfect and there is no failure of them.

- When a train moves through a joint, the modification of track segment is automatically recorded.

- Communication between several interlockings is not considered.

- The level crossing control and its interaction with the routes is not modelled. A level crossing is an intersection between a railway line and a road.

These assumptions are mainly done in order to keep the model as simple as possible and then limit the state space size. Such assumptions are also proposed in other works [5, 35, 36].

# 3.5 Train model

The previous section introduced how we modelled an interlocking system. Let us remember that the goal of an interlocking system is to ensure a safe and fluid train traffic. However, until now the train traffic is not yet considered. This section describes how we model trains. As proposed in different works [5, 35, 36], our modelling is based on several assumptions:

- Trains follows properly the signalling principles. For instance, they do not overrun signals on a stop state.

- Speed and length of trains are abstracted.

- Trains just occupy one and only one track segment at a time.

- Trains can stop instantly.

- Trains have a perfect behaviour. They have no faulty component and have no train failure.

- Trains only enter in the station from buffer stops.

Furthermore, the model contains three attributes:

- An identifier: each train has an unique identifier.

- A **position**: it defines the track segment where the train is located.

- A direction: it defines the direction of the train. It has two possible values, up or down.

Furthermore, trains only move from track segment to track segment until they reach the end of the station. As we will see in the next section, this model is used in order to build a mutable entity which can be simulated. The interlocking model is then tested with a traffic composed of trains modelled in this way.

# 3.6 Signalman model

The next step is to model the signalman. Generally speaking, the signalman is the human who sets the signals and the points in order to control the train traffic. For modern route based interlockings, the signalman has the responsibility for performing route request when trains enter into the station.

In our case, we model the signalman as an object without attributes but which performs route requests for trains waiting at a start signal of a route.

# 3.7 Simulator

Simulation is a science used everyday and applied to a large number of fields such as weather forecasting [37], transportation [38], logistic [39] or healthcare facilities [40, 41]. It has also been applied to the railway field. For instance, Sogin et al. [42] analyse through simulation the effects of higher speed passenger trains in freight networks. Furthermore, the company OpenTrack provides a railway simulation tool [43] to verify the capacity of a railway network, the feasibility of the schedules, collect statistics about running times, etc. Generally speaking, a simulation can be defined as an imitation of a system [44]. The main force of simulation is that it allows the study of various systems without building the system, thus saving precious time, cost and effort. Real life includes myriads of systems. Checkland [45] identified four classes:

- Natural systems: they are the systems created from the origins of the universe (weather, movements of planets, etc.).

- **Designed physical systems**: they are the physical systems created from the result of a human design (production facility, transportation network, etc.).

- **Designed abstract systems**: they are the abstract systems created from the result of a human design (mathematics, literature, etc.).

- Human activity systems: they are the systems modelling human activities with their interactions (political system, communication, etc.).

All of these systems can be modelled and then be simulated. In our case, we are interested by *interlockings*, a specific designed physical system. The previous section described how this system can be modelled. This section presents how its simulation can be performed. Firstly, generalities about simulation are presented. The principles of our simulation is then described. Finally, the integration of this simulation and its application for our railway model is detailed.

#### 3.7.1 Simulation taxonomy

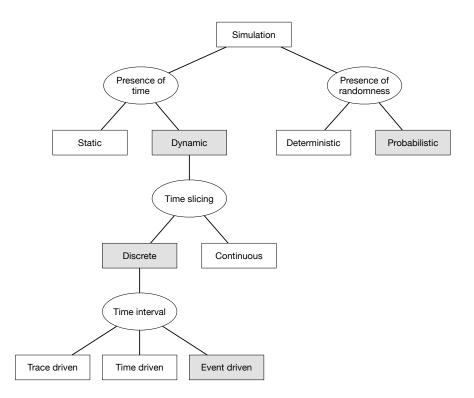

A simulation can be performed in a plenty of ways. According to the considered system, some kinds of simulation can be more adapted than others. Sulistio et al. [46] identified several inherent characteristics of simulation:

- **Presence of randomness** A simulation can be either **deterministic** or **stochastic** according to the presence of randomness or not. In deterministic simulations, there is no randomness. It means that for a given input, the output will always be the same. In stochastic simulations, the output can be different for a same input.

- **Presence of time** Time can be considered in the simulation or not. A **static simulation** imitates a system at a particular point in time while a **dynamic simulation** imitates the system with its progression in time.

- **Time slicing** When time is considered, it can be represented in two ways. Firstly, there are the **continuous simulations** which consider an infinity of values through a bounded time interval. Secondly, they are the **discrete simulations** which discretise the time into instants. A time interval T from 0 to 4 seconds can for instance

be discretised into 0, 1, 2, 3, 4 seconds and then produce 5 values. For the same interval, a continuous simulation would produce an infinity of values.

**Time interval** For discrete simulations, the management of time intervals can be done in different ways:

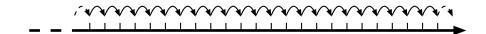

• **Time driven simulation**: the simulation progresses by fixed time increments. Figure 3.6 illustrates this process.

Figure 3.6. Behaviour of a time driven simulation.

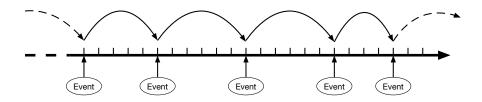

• Event driven simulation: the simulation progresses by irregular time increments according to the execution instant of the events. An event can be defined as a modification on the system state. If there is no event planned for a particular instant, it will then not be considered. Figure 3.7 illustrates this process.

Figure 3.7. Behaviour of an event driven simulation.

• **Trace driven simulation**: the simulation progresses by reading a set of events collected from another environment and that has been previously executed.

Figure 3.8 illustrates such taxonomy. The grey boxes represent the choices made for our system. As we can see, our simulation follows a probabilistic dynamic discrete event pattern. However, the *dynamic*

#### 3.7. SIMULATOR

and *probabilistic* attributes are often implicit in computer simulation. It is why this kind of simulation is often shorted as a **discrete event** simulation (DES) [47].

Figure 3.8. Simulation taxonomy with the choices made for our system (in grey).

#### 3.7.2 Principles of discrete event simulation

This section describes the principles of a discrete event simulation and presents how it can be implemented. A discrete event simulation involves five kinds of components:

**Entities** They are the active objects on which the simulation is applied. Each entity is characterised by a list of attributes with a specific value. This list is called the **entity state**. The term *active*

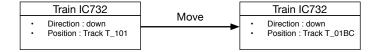

means that the value of attributes can change through time. For instance, a train can be an entity characterised by a direction and a position. Figure 3.9 illustrates how we represent Train IC732 entity.

Using a programming language supporting the object oriented paradigm such as Java or Scala, an entity schema can be implemented as a *class* and an entity as an *object*.

|   | Train IC732            |

|---|------------------------|

| • | Direction : down       |

| • | Position : Track T_101 |

|   |                        |

Figure 3.9. Train IC732 entity.

**Events** They define the actions that can change the entity state and which can generate other events.

**Definition 3.2** (Event). In a simulation, an event is an action changing the system state. It is characterised by two attributes:

- The action.

- The time at which the action must be executed.

For an event e, e.process is the action and e.time is its execution time. For instance, we can consider an event which applies on a train entity and which moves the train to its next position. Figure 3.10 illustrates this behaviour. A guard can also be present for events. It defines conditions that must be satisfied for activating the event. For instance, let us consider a situation where a train is waiting in front of a signal. The event can be triggered only if the signal is on its proceed state.

Figure 3.10. move event applied to Train IC732.

- **Clock** It states when the events must be executed. Unlike a continuous simulation where events can occur during a time period, the discrete simulation requires each event to occur at a particular instant. Furthermore, it is used to model the progression of the simulation through time. For an event based simulation, this mechanism is often organized as a priority queue [48], sorted by event time. Jones [49] proposes several implementations for it. With such a data structure, the next event to be executed is the event with the closest event time from the actual time of the simulation.

- **Pseudo random number generator** As previously said, this simulation is probabilistic. It means that two simulations from identical inputs can have a different progression. Such a mechanism requires to generate randomness. However, generating pure random variables with a computer is not feasible [50]. For this reason, the use of a Pseudo Random Number Generator (PRNG) [51] is required.

**Definition 3.3** (Pseudo Random Number Generator). A PRNG is an algorithm used for generating from an initial value called the seed, a sequence of numbers which looks like a sequence of numbers randomly picked up.

For a given seed, a PRNG always produces the same sequence. The choice is the seed is then crucial. It is often determined by unpredictable parameters having a high level of entropy such as the exact timing of keystrokes and the movements of the computer mouse [52]. There exists a large variety of PRNG in the literature [53, 54, 55, 56], each having their own specificities.

**Ending condition** It states when the simulation must end. Typically, we end the simulation after a given number of iterations or after that a particular state has been reached. For instance, we can stop the simulation after that an accident has occurred.

Each of these components must be implemented in order to have a discrete event simulation engine.

## 3.7.3 Simulator architecture

The design of our simulator is then based on the discrete event paradigm. This section presents the architecture of the simulator and describes its different components. Firstly, Figure 3.11 gives an overview of this architecture. A description of each component is provided thereafter.

Figure 3.11. Simulator architecture.

**Interlocking model** The interlocking model is the model built from the aggregation of the application data and the station topology as presented in Section 3.4. It is used to infer a bunch of entities. Concretely each interlocking component is represented as an entity.

**Definition 3.4** (Interlocking entity). An interlocking entity is an entity obtained from the interlocking active components.

The exhaustive list of interlocking entities with their mutable attributes is as follows:

- The routes, on a free, commanded or activated state.

- The signals, on a proceed or stop state.

- The points, on a normal or reverse position.

- The subroutes, immobilisation zones and bidirectional locking, each of them on a free or locked state.

- The track segments, characterised by the number of trains on it.

**Train model** In the same way than the interlocking model, the train model is the model described in Section 3.5. The **train** entity if inferred from it.

**Definition 3.5** (Train entity). A train entity is an entity obtained from the train model. It is characterised by two mutable attributes: a position (the current track segment occupied by the train) and a direction (up or down). Each train is identified by a unique identifier (id).

**Signalman model** It is the model of the signalman performing the route requests.

**PRNG** Given that randomness is present in the simulation, a PRNG is thereby required. To do so, a linear congruential generator [57] with a 48-bit seed is used.

**Definition 3.6** (Linear congruential generator). A linear congruential generator is an algorithm used in order to generate a sequence of pseudo random numbers. It is based on the following recurrence relation:

$$X_{n+1} = (aX_n + b) \mod m$$

where a, b and m are parameters. The next number in the sequence is then determined by its previous number.

An implementation is available in java.util.Random package for Java or Scala. This implementation can generate numbers with a uniform probability. Given that we use randomness only to generate different scenarios through simulations, we are not concerned by having a strict unpredictable sequence of number or a cryptographically secure generator [58]. The choice of the PRNG is then not a critical concern.

**Event list** The event list contains all the events that will be processed through the simulation. The simulation contains two kinds of events: events related to train movements and events related to interlocking actions.

**Definition 3.7** (Train event). A train event is an event related to the actions that the trains perform from their arrival in the station to their departure.

There are three train events:

- addTrain(t,bf): this event adds a new train called t at the bufferStop called bf (Section 2.5). The station state is updated accordingly. Furthermore, it triggers two events: another addTrain event and a moveTrain event. The execution time of such events is determined by the PRNG.

- moveTrain(t): this event moves Train t to its next position on the station and updates the station accordingly. Trains always move upside or downside according to their direction, from one track segment to the next one and follow the path defined by the points. If t is in front of a signal on a stop state, the train will not move. In any case, this event triggers one of the following event: another moveTrain or a removeTrain if the train has reached a bufferStop. The execution time is also determined by the PRNG.

- removeTrain(t): this event is triggered by a moveTrain event only if Train t is in front of a bufferStop. Such an event removes t of the station and updates it accordingly.

With such events, each train has thereby its own queue of events going from addTrain to removeTrain with a sequence of moveTrain.

There are also the interlocking events.

**Definition 3.8** (Interlocking event). An interlocking event is an event related to the actions that the interlocking can perform.

An interlocking event can be one of the following types:

• generateRoute(r): this event is periodically issued for the trains waiting at a start point of Route r. If the route command conditions are fulfilled, r is commanded and all the actions described in the request are executed as well as the related bidirectional locking request. The station state will then change. Otherwise, the request is discarded and no action is taken. Route command requests are described in the application data, as presented in Listings 2.1, 2.2 and 2.3.

#### 3.7. SIMULATOR

- activateRoute(r): this event is periodically issued when Route r is already commanded but not activated yet. If the conditions are fulfilled, r is activated (Listing 2.4). Otherwise, the request is discarded and no action is taken. Furthermore, after three unsuccessful activation requests for the same route, a destroyRoute event for r is triggered.

- destroyRoute(r): this event performs a hard release of Route r and unlocks each component previously requested by the route.

- releaseComponents: this event tries to release every locked component on the station (Listing 2.5). If the conditions are not fulfilled, no action is taken. Such an event is periodically issued and before each train movement.

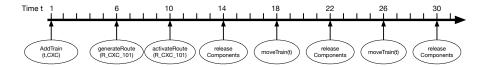

As for the train events, the execution time of all interlocking events is determined by the PRNG. Furthermore, their execution also triggers another event of the same type. Figure 3.12 illustrates a possible scenario.

Figure 3.12. Possible scenario with the simulator.

The event list is ordered using a priority queue, sorted by event time. We use the default implementation proposed by the Scala API (scala.collection.mutable) which uses a heap data structure [59]. A priority queue contains two main instructions: add(Event e) which adds the event e inside the queue, and pop() which removes from the queue the event with the highest priority and returns it. Before the simulation, the event queue is fed with initial events.

**Simulation model** The simulation model is obtained from the aggregation of the interlocking model, the train model, the signalman model, the PRNG and the event list. It is the model which can be simulated. Concretely, it gathers the information of the inputs into a **simulation state**. The simulation state  $s_i$  is a description of the considered station at the  $i^{th}$  simulation step. It can change after each event which has occurred during the simulation. For a simulation of n steps, a simulation state  $s_i$  with  $i \in [1, n]$  is defined as

$$s_i: \langle nb, \sigma_p, \sigma_r, \sigma_s, \sigma_{uir}, \sigma_{ubsi}, \sigma_{track}, \sigma_{train} \rangle$$

$$(3.1)$$

where

- $s_i$  is the state at the  $i^{th}$  step of the simulation.

- *nb* is the number of trains that have moved in the station so far. This variable is used to under approximate how many real days the simulation has covered. Indeed, by taking the extreme case of a busy station where there is an incoming train every minute all the day long, we can safely assume that the simulation has covered at least one real day when 1440 trains have moved through the station.

- $\sigma_p$ : point  $\rightarrow$  {normal, reverse, default} is a function defining the position of a point. The default state represents a point that is not positioned yet.

- $\sigma_r : \text{route} \rightarrow \{\text{unset}, \text{commanded}, \text{activated}\}$  is a function defining the state of a route.

- $\sigma_s$ : subroute  $\rightarrow$  {free, locked} is a function defining if a subroute is free or locked.

- $\sigma_{uir} : uir \rightarrow \{ free, locked \}$  is a function defining if an immobilisation zone is free or locked.

- $\sigma_{ubsi}$ : ubsi  $\rightarrow$  {free, locked} is a function defining if a bidirectional locking is free or locked.

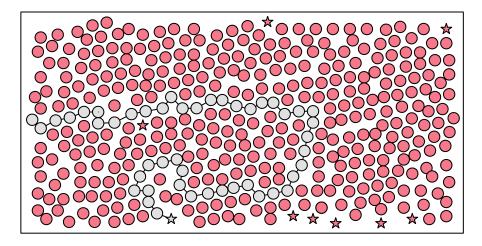

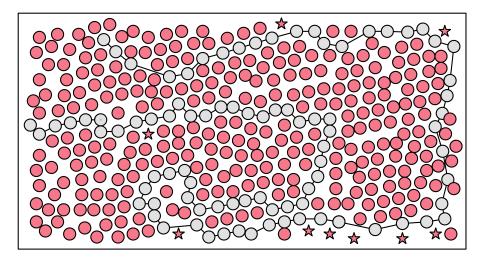

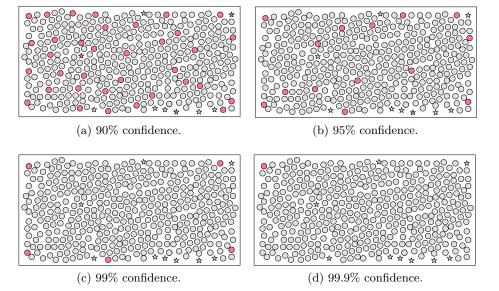

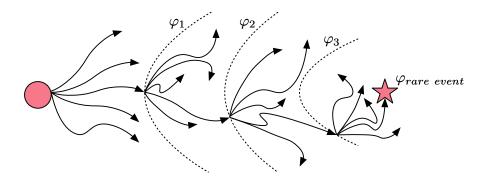

- $\sigma_{track}$  : track  $\rightarrow \mathbb{N}$  is a function defining the number of trains being on a track segment.